1同步十进制加法计数器一实验目的(1)学会Pspice软件的使用,会用Pspice软件对电路进行仿真

(2)掌握时序电路的设计方法

(3)提高分析、动手解决实际问题的能力

二实验环境(1)软件环境:WindowsXP操作系统,Pspice软件

(2)硬件环境:Pentium以上的计算机

(3)JK触发器4片、双输入单输出与门芯片4片、三输入单输出芯片1片、时钟信号源2个、高电平信号1个

三实验原理同步时序电路的设计过程可由图1-1描述

首先将实际逻辑问题进行抽象——确定输入、输出变量及电路的状态数,对变量逻辑赋值,对状态编号,从而得到一个反应时序问题的状态装换图

去掉重复状态(若有重复的话),且对状态编码,则得到状态转换图的最简形式

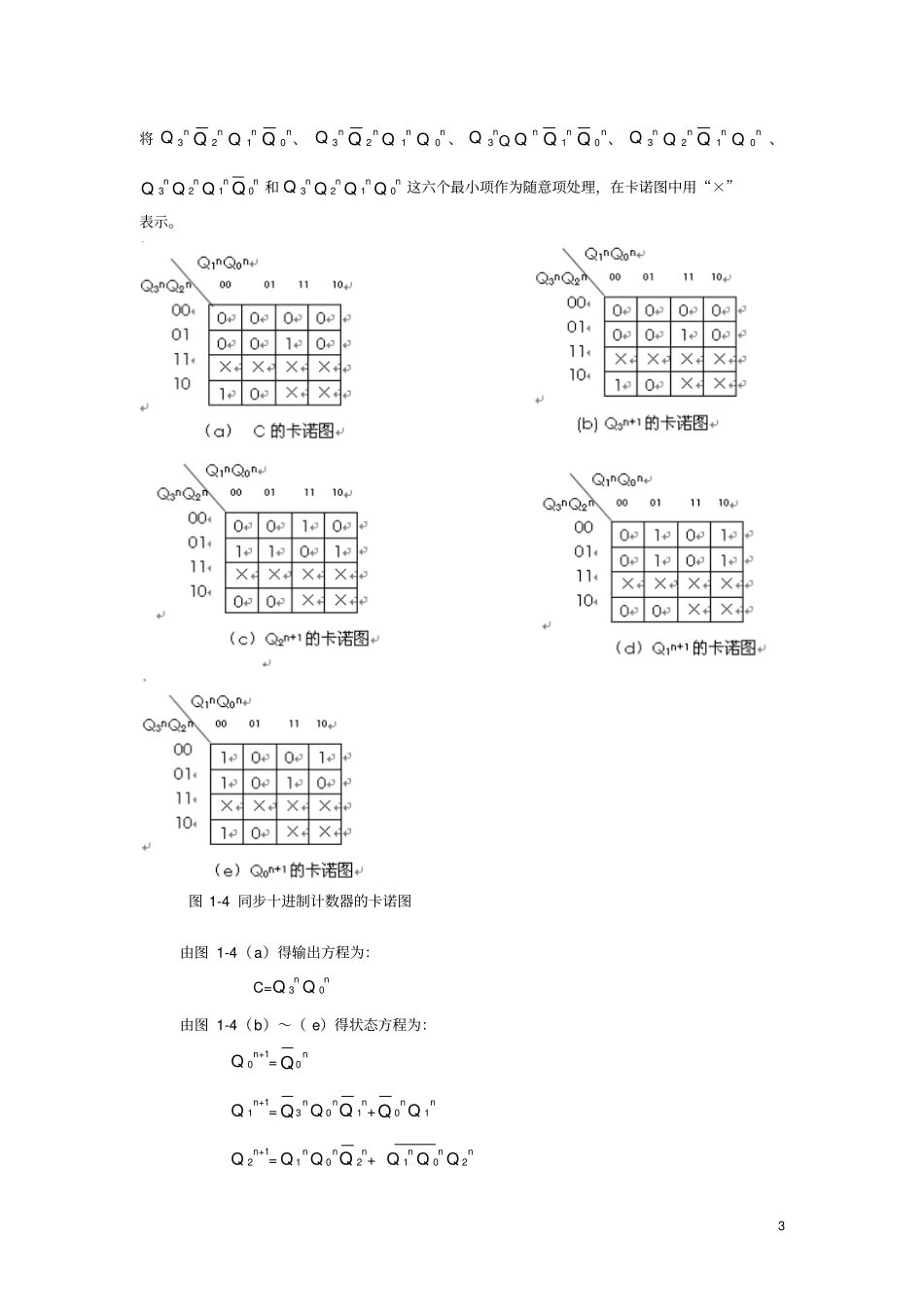

对图化简得到电路的状态方程与输出方程,选定触发器类型后,则有状态方程求出驱动方程

最后根据驱动与输出方程画出逻辑原理图、实验电路图

根据实验电路图连线、调试并验证电路功能

检查电路能否自启动,若不能则应修改设计或预置初值解决

确定触发器类型检查自启动图1-1时序电路的设计过程四实验内容与步骤1、根据时间问题当数字每满十置零一次,根据BCD码原则需要用四位二进制来表示,因此,需要选择4个触发器,其状态表如表1-2所表示:时序逻辑问题状态转换图最简状态转换图电路方程实验电路图2Q3nQ2nQ1nQ0n+1Q3n+1Q2n+1Q1n+1Q0n+1C000000010000100100001000110001101000010001010010101100011001110011110000100010010100110101101010110101111001110011010110111101111011110111100001表1-2同步十进制加法器状态表2、根据状态表画出的该计数器的状态图如下:/1/0/0/0/0/1/0/C/0/1排列:/0