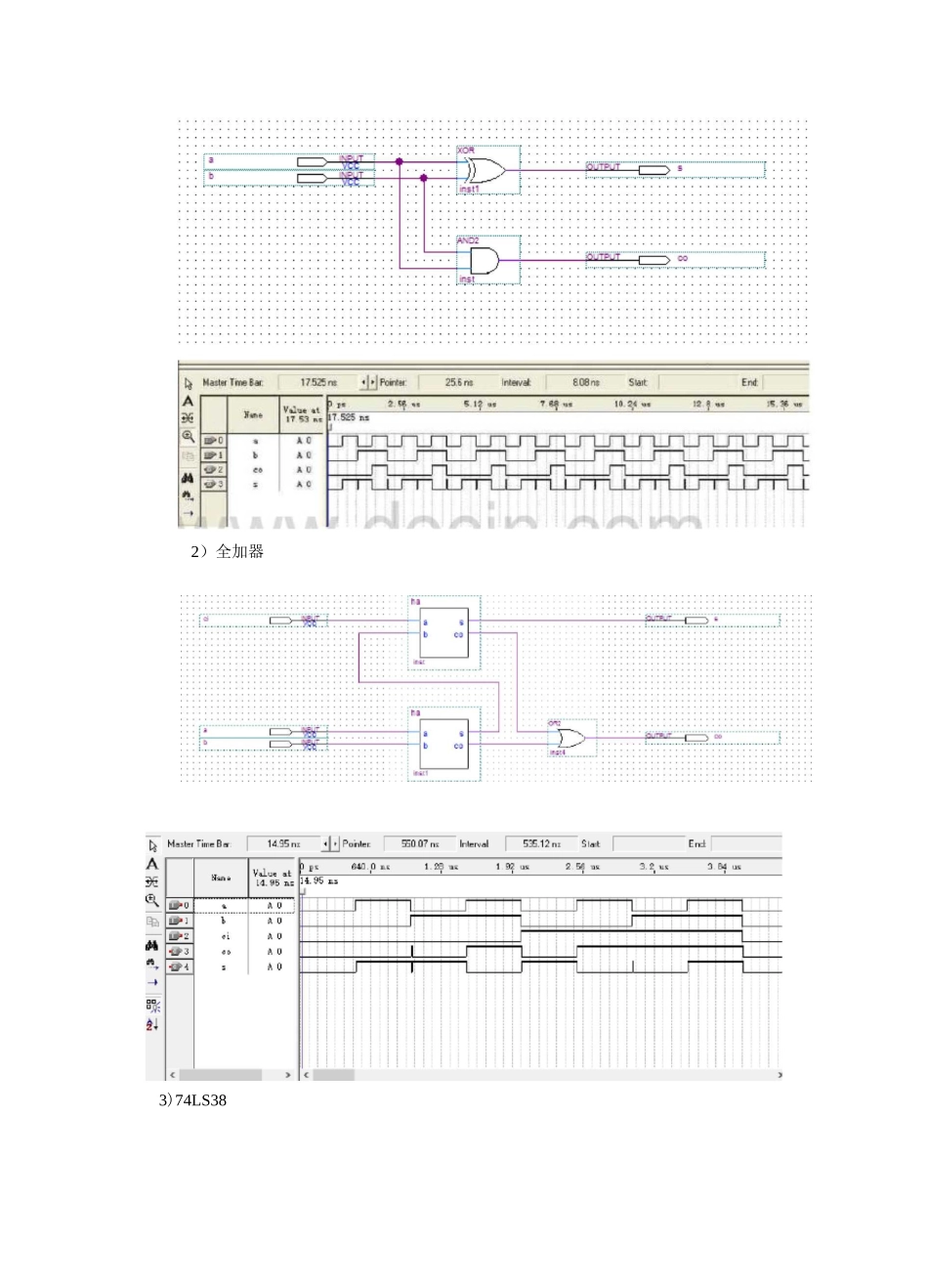

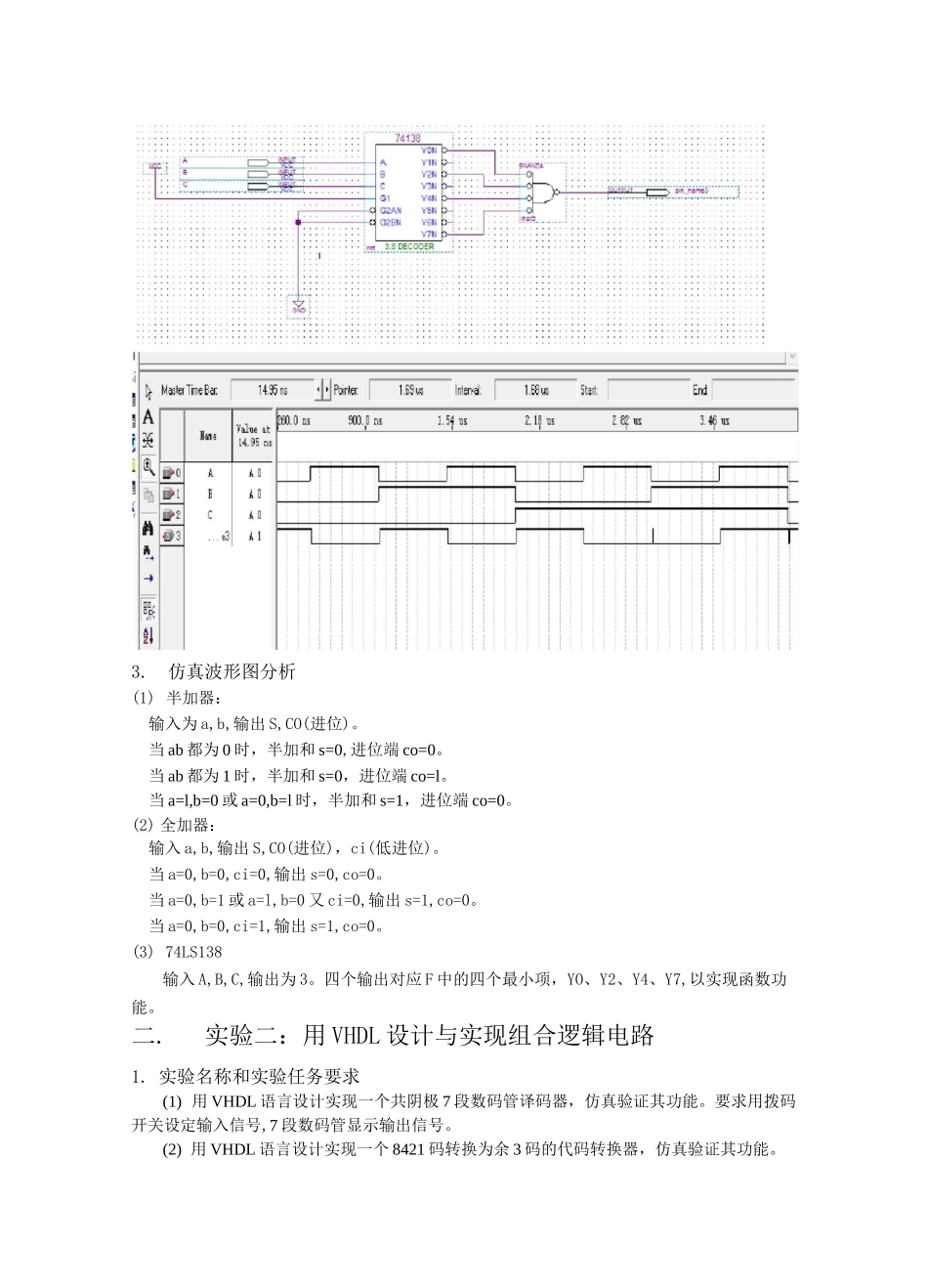

实实验名称:辑设计实验北京邮电大学学院:信息与通信工程学院班级:姓名:学号:_班内序号:日期:一.实验一:QuartusII原理图输入法设计1.实验名称和实验任务要求(1)用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块元。(2)用(1)中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号入信号。⑶用3线-8线译码器(74LS138)和逻辑门设计实现函数F=CBA+CBA+CBA+CBA。2.实验原理图及波形图(1)半加器2)全加器3)74LS383.仿真波形图分析(1)半加器:输入为a,b,输出S,CO(进位)。当ab都为0时,半加和s=0,进位端co=0。当ab都为1时,半加和s=0,进位端co=l。当a=l,b=0或a=0,b=l时,半加和s=1,进位端co=0。(2)全加器:输入a,b,输出S,CO(进位),ci(低进位)。当a=0,b=0,ci=0,输出s=0,co=0。当a=0,b=1或a=l,b=0又ci=0,输出s=1,co=0。当a=0,b=0,ci=1,输出s=1,co=0。(3)74LS138输入A,B,C,输出为3。四个输出对应F中的四个最小项,YO、Y2、Y4、Y7,以实现函数功能。二.实验二:用VHDL设计与实现组合逻辑电路1.实验名称和实验任务要求(1)用VHDL语言设计实现一个共阴极7段数码管译码器,仿真验证其功能。要求用拨码开关设定输入信号,7段数码管显示输出信号。(2)用VHDL语言设计实现一个8421码转换为余3码的代码转换器,仿真验证其功能。要求用拨码开关设定输入信号,发光二极管显示输出信号。(3)用VHDL语言设计实现一个4位二进制奇校验器,输入奇数个'1'时,输出为'1',否则输出'0',仿真验证其功能。要求用拨码开关设定输入信号,发光二极管显示输出信号。2.实验代码及波形图(1)共阴极7段数码管译码器LIBRARYIEEEUSEIEEE.STD_LOGIC_1164.ALLUSEIEEE.STD_LOGIC_UNSIGNED.ALLENTITYGUANISPORT(A:INSTD_LOGIC_VECTOR(3DOWNTO0)B:OUTSTD_LOGIC_VECTOR(6DOWNTO0)C:OUTSTD_LOGIC_VECTOR(5DOWNTOO))ENDGUANARCHITECTUREencoder_archOFGUANISBEGINPROCESS(A)BEGINC<="011111"CASEAISWHEN"0000"=>B<="1111110"--0WHEN"0001"=>B<="0110000"--1WHEN"0010"=>B<="1101101"--2WHEN"0011"=>B<="1111001"--3WHEN"0100"=>B<="0110011"--4WHEN"0101"=>B<="1011011"--5WHEN"0110"=>B<="1011111"--6WHEN"0111"=>B<="1110000"--7WHEN"1000"=>B<="1111111"--8WHEN"1001"=>B<="1111011"--9WHENOTHERS=>B<="ZZZZZZZ"ENDCASEENDPROCESSENDencoder_arch(2)8421码转换为余3码LIBRARYIEEEUSEIEEE.STD_LOGIC_1164.ALLUSEIEEE.STD_LOGIC_UNSIGNED.ALLENTITYYUSANISPORT(A:INSTD_LOGIC_VECTOR(3DOWNTO0)B:OUTSTD_LOGIC_VECTOR(3DOWNTOO))ENDYUSANARCHITECTUREtrans_ex3OFYUSANISBEGINPROCESS(A)BEGINCASEAISWHEN"0000"=>B<="0011"WHEN"0001"=>B<="0100"WHEN"0010"=>B<="0101"WHEN"0011"=>B<="0110"WHEN"0100"=>B<="0111"WHEN"0101"=>B<="1000"WHEN"0110"=>B<="1001"WHEN"0111"=>B<="1010"WHEN"1000"=>B<="1011"WHEN"1001"=>B<="1100"WHENOTHERS=>B<="ZZZZ"ENDCASEENDPROCESSENDtrans_ex3MacteiTinreBai:7&1U.E世—gi.胡2'l虬hnMiW"filIT吶——I(3)4位二进制奇校验器LIBRARYIEEEUSEIEEE.STD_LOGIC_1164.ALLENTITYJIOUISPORT(a,b,c,d:INSTD_LOGICy:OUTSTD_LOGIC)ENDJIOUARCHITECTUREbehavOFJIOUISBEGINPROCESS(a,b,c,d)VARIABLEcomb:STD_LOGIC_VECTOR(3DOWNTO0)BEGINcomb:=a&b&c&dCASEcombISWHEN"0000"=>y<='0'WHEN"0001"=>yv=TWHEN"0010"=>yv=TWHEN"0011"=>y<='0'WHEN"0100"=>yv=TWHEN"0101"=>y<='0'WHEN"0110"=>y<='0'WHEN"0111"=>yv=TWHEN"1000"=>yv=TWHEN"1001"=>y<='0'WHEN"1010"=>y<='0'WHEN"1011"=>yv=TWHEN"1100"=>y<='0'WHEN"1101"=>yv=TWHEN"1110"=>yv=TWHEN"llll"=>yv='O'WHENOTHERS=>y<='0'日A-A[3]-M2】-A[LJLA[O]□B-E[3]■B[2]-B[L]-B[OJ17.525n&Pcrilef:E.45usInleri■吐6.13u$Starl:EnENDCASEENDPROCESS3.仿真波形分析(1)8421码转为余三码:输出在输入基础上加Oil(2)四位二进制奇校验码:当输入有奇数个一时,输出1,偶数个一时,输出0。三.实验三:用VHDL设计与实现组合逻辑电路1.实验名称和实验任务要求(1)用...