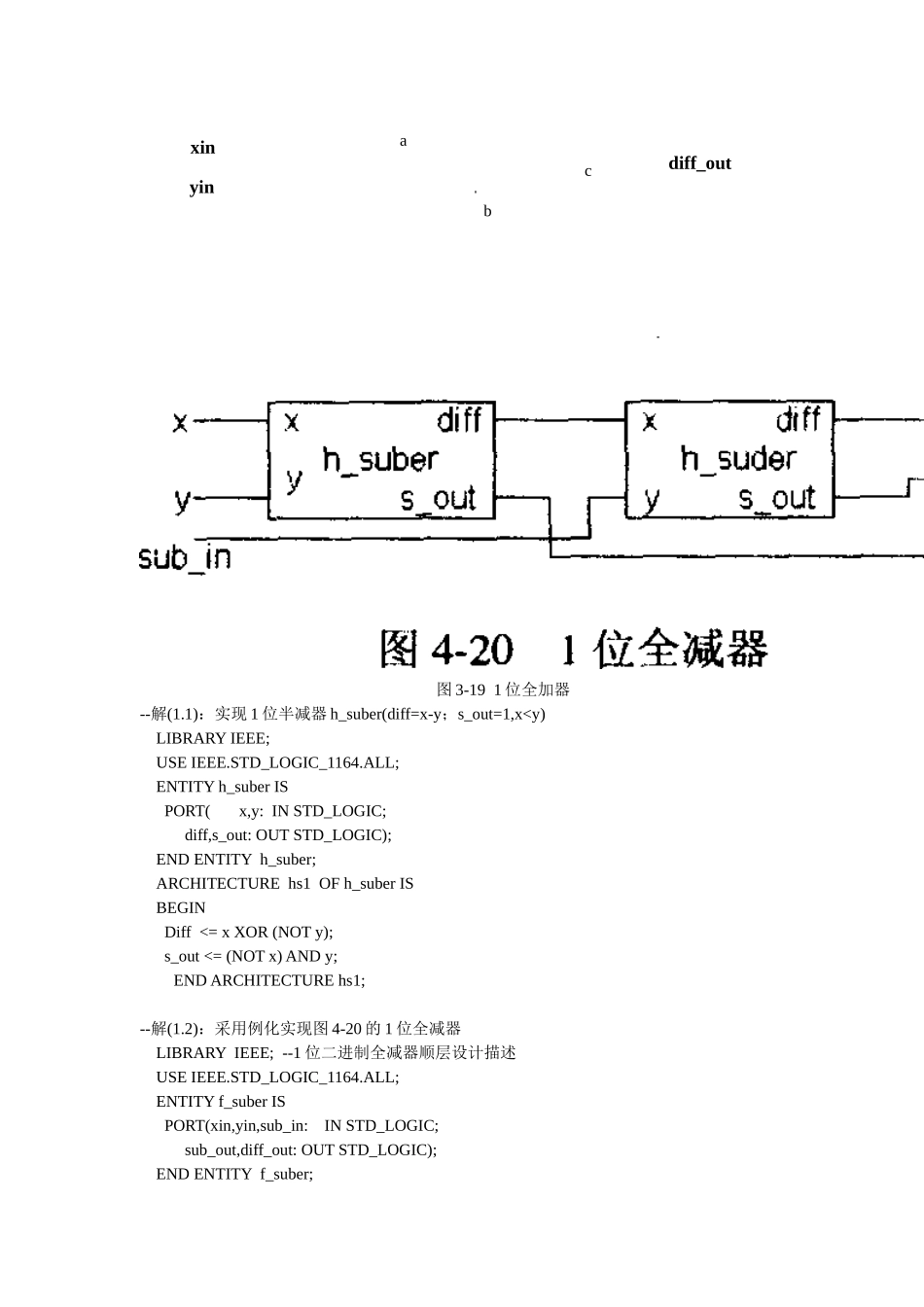

3-3给出一个4选1多路选择器的VHDL描述。选通控制端有四个输入:S0、S1、S2、S3。当且仅当S0=0时:Y=A;S1=0时:Y=B;S2=0时:Y=C;S3=0时:Y=D。--解:4选1多路选择器VHDL程序设计。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYmux41aISPORT(A,B,C,D:INSTD_LOGIC;S0,S1,S2,S3:INSTD_LOGIC;Y:OUTSTD_LOGIC);ENDENTITYmux41a;ARCHITECTUREoneOFmux41aISSIGNALS0_3:STD_LOGIC_VECTOR(3DOWNTO0);BEGINS0_3<=S0&S1&S2&S3;y<=AWHENS0_3="0111"ELSEBWHENS0_3="1011"ELSECWHENS0_3="1101"ELSEDWHENS0_3="1110"ELSE'Z';ENDARCHITECTUREone;3-4给出1位全减器的VHDL描述;最终实现8位全减器。要求:1)首先设计1位半减器,然后用例化语句将它们连接起来,图4-20中h_suber是半减器,diff是输出差(diff=x-y),s_out是借位输出(s_out=1,xxin,y=>yin,diff=>a,s_out=>b);u2:h_suberPORTMAP(x=>a,y=>sub_in,diff=>diff_out,s_out=>c);sub_out<=cORb;ENDARCHITECTUREfs1;(2)以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是x-y-sun_in=difft)。--解(2):采用例化方法,以1位全减器为基本硬件;实现串行借位的8位减法器(上图所示)。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYsuber_8ISPORT(x0,x1,x2,x3,x4,x5,x6,x7:INSTD_LOGIC;y0,y1,y2,y3,y4,y5,y6,y7,sin:INSTD_LOGIC;diff0,diff1,diff2,diff3:OUTSTD_LOGIC;diff4,diff5,diff6,diff7,sout:OUTSTD_LOGIC);ENDENTITYsuber_8;ARCHITECTUREs8OFsuber_8ISCOMPONENTf_suber--调用全减器声明语句PORT(xin,yin,sub_in:INSTD_LOGIC;sub_out,diff_out:OUTSTD_LOGIC);ENDCOMPONENT;SIGNALa0,a1,a2,a3,a4,a5,a6:STD_LOGIC;--定义1个信号作为内部的连接线。xinsub_outyinu0sub_indiff_outx0y0sindiff0xinsub_outyinu1sub_indiff_outx1y1diff1xinsub_outyinu7sub_indiff_outx7y7soutdiff7……………….……………….串行借位的8位减法器a0a1a6BEGINu0:f_suberPORTMAP(xin=>x0,yin=>y0,diff_out=>diff0,sub_in=>sin,sub_out=>a0);u1:f_suberPORTMAP(xin=>x1,yin=>y1,diff_out=>diff1,sub_in=>a0,sub_out=>a1);u2:f_suberPORTMAP(xin=>x2,yin=>y2,diff_out=>diff2,sub_in=>a1,sub_out=>a2);u3:f_suberPORTMAP(xin=>x3,yin=>y3,diff_out=>diff3,sub_in=>a2,sub_out=>a3);u4:f_suberPORTMAP(xin=>x4,yin=>y4,diff_out=>diff4,sub_in=>a3,sub_out=>a4);u5:f_suberPORTMAP(xin=>x5,yin=>y5,diff_out=>diff5,sub_in=>a4,sub_out=>a5);u6:f_suberPORTMAP(xin=>x6,yin=>y6,diff_out=>diff6,sub_in=>a5,sub_out=>a6);u7:f_suberPORTMAP(xin=>x7,yin=>y7,diff_out=>diff7,sub_in=>a6,sub_out=>sout);ENDARCHITECTUREs8;3-8设计一个求补码的程序,输入数据是一个有符号的8位二进制(原码)数。--解:5-9设计一个求补码的程序,输入数据是一个有符号的8位二进制数。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYorg_patchISPORT(org_data:INSTD_LOGIC_VECTOR(7DOWNTO0);--原码输入patch_data:OUTSTD_LOGIC_VECTOR(7DOWNTO0));--补码输出ENDorg_patch;ARCHITECTUREBHVOForg_patchISBEGINPROCESS(org_data)BEGINIF(org_data(7)='0')THENpat...