A1B1A0B0+C1S1S0一、典型例题及其讲解例 8

1 可编程逻辑阵列(PLA)实现的组合逻辑电路如图 8

(1)分析电路的功能,写出 F1~F3 的表达式;(2)若已知 A1A0,B1B0为两个两位的二进制数,试证明电路实现的是二位二进制全加运算

(3)说明电路矩阵的容量,若改用 PROM 实现此电路,则矩阵的容量又应为多

解:PLA 和 PROM 的结构大体相同 , 不 同 的 PLA 无 论 是 “ 与 阵列”还是“或阵列”均为编程结构,而 PROM 的“与阵列”为固定的,不可编程的结构,只有“或阵列”是可编程的

因此,在实现同一函数时,PLA 通常要比 PROM 所用的矩阵容量少

1 、 根 据 图 8

1 中 PLA“ 与 ” ,“或”阵列输入,输出的关系,可直接得到输出函数 F1~F3的表达式,即:F1=A0B0+A0B0F2=A1A0 B1B0+A1 A0 B1 B0+A1A0⋅B1+A1⋅A0 B1+A1B1⋅B0+A1B1B0F3=A1B1+A1 A0B0+A0 B1 B02、若 A1A0,B1B0为两位二进制的加数,则满足运算规则 其中 {S0=A0⊕B0¿{S1=A1⊕B1⊕C0¿{C1=A1B1+(A1⊕B1)C0¿¿¿¿ 将S0 S1C1写成“与”“或”式有:{S0=A0B0+A0B0¿{S1=A1A0B1B0+A1A0B1B0+A1A0B1+A1A0B1+A1B1B0+A1B1B0¿¿¿¿ (8

1) ∴F1=S0 F2=S1 F3=C1 故电路实现的是两位二进制全加器3、由图 8

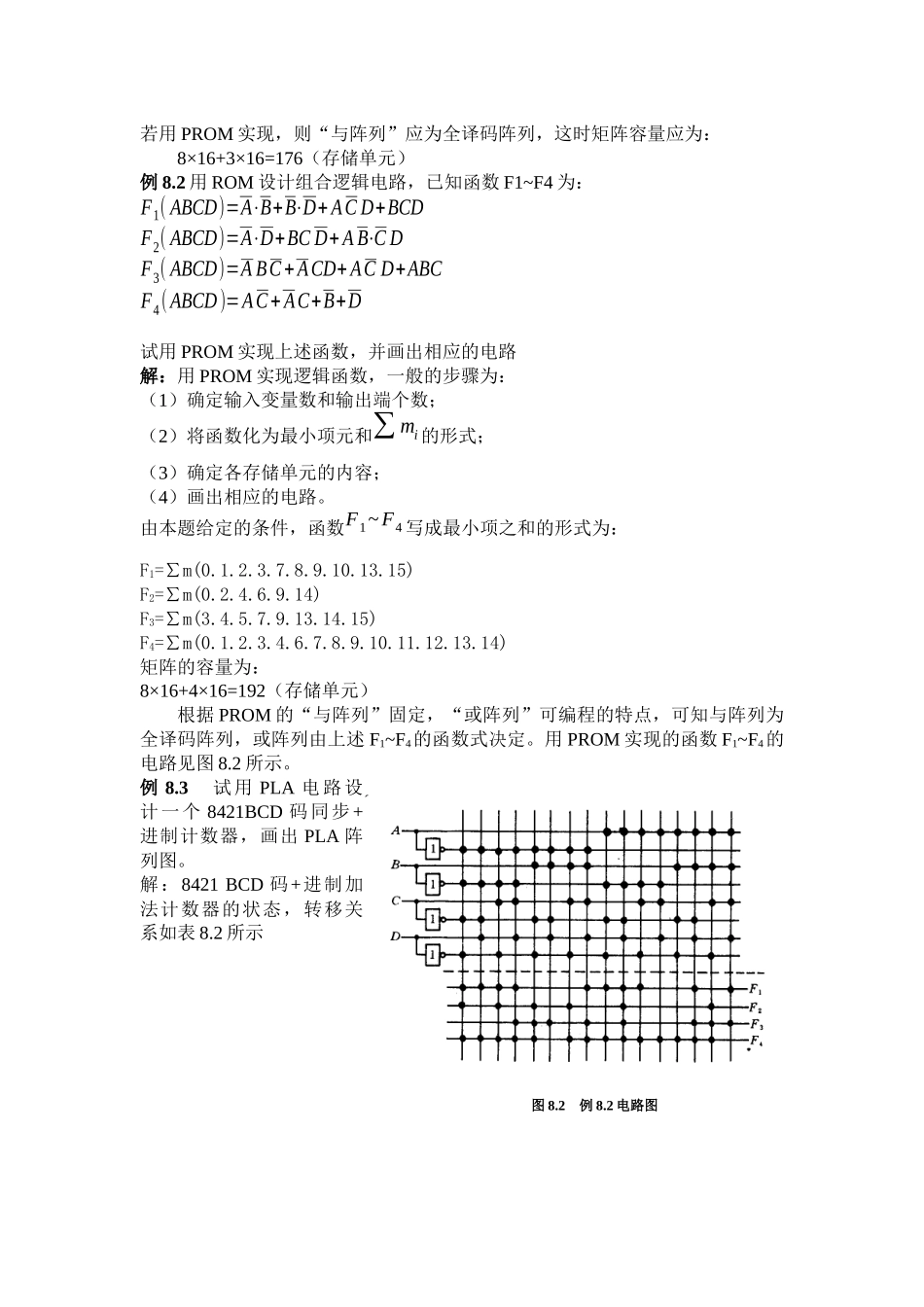

1 电路可知,矩阵的容量为8×11+3×11=121(存储单元)的逻辑电路若用 PROM 实现,则“与阵列”应为全译码阵列,这时矩阵容量应为:8×16+3×16=176(存储单元)例 8

2 用 ROM 设计组合逻辑电路,已知函数 F1~F4 为:F1