1 EDA期末复习题一、单选题1、下面即是并行语句又是串行语句的是()A

PROCESS 语句D

WHEN ⋯ELSE 语句2、 下列 EDA 软件中,哪一个不具有逻辑综合功能()A

Max+Plus II B

ModelSim C

Quartus II D

Synplify 3、 在 Quartus9

0 中锁定引脚的操作是()A

Assignments →> Pins B

Assignments→> Settings C

Assignments→>Device D

Processing→>Pins 4、 将 STD_LOGIC_VECTOR类型转换成INTEGER 类型的语句是()A

CONV_STD_LOGIC_VECTOR() B

CONV_INTEGER() C

CONVERT_STD_LOGIC_VECTOR() D

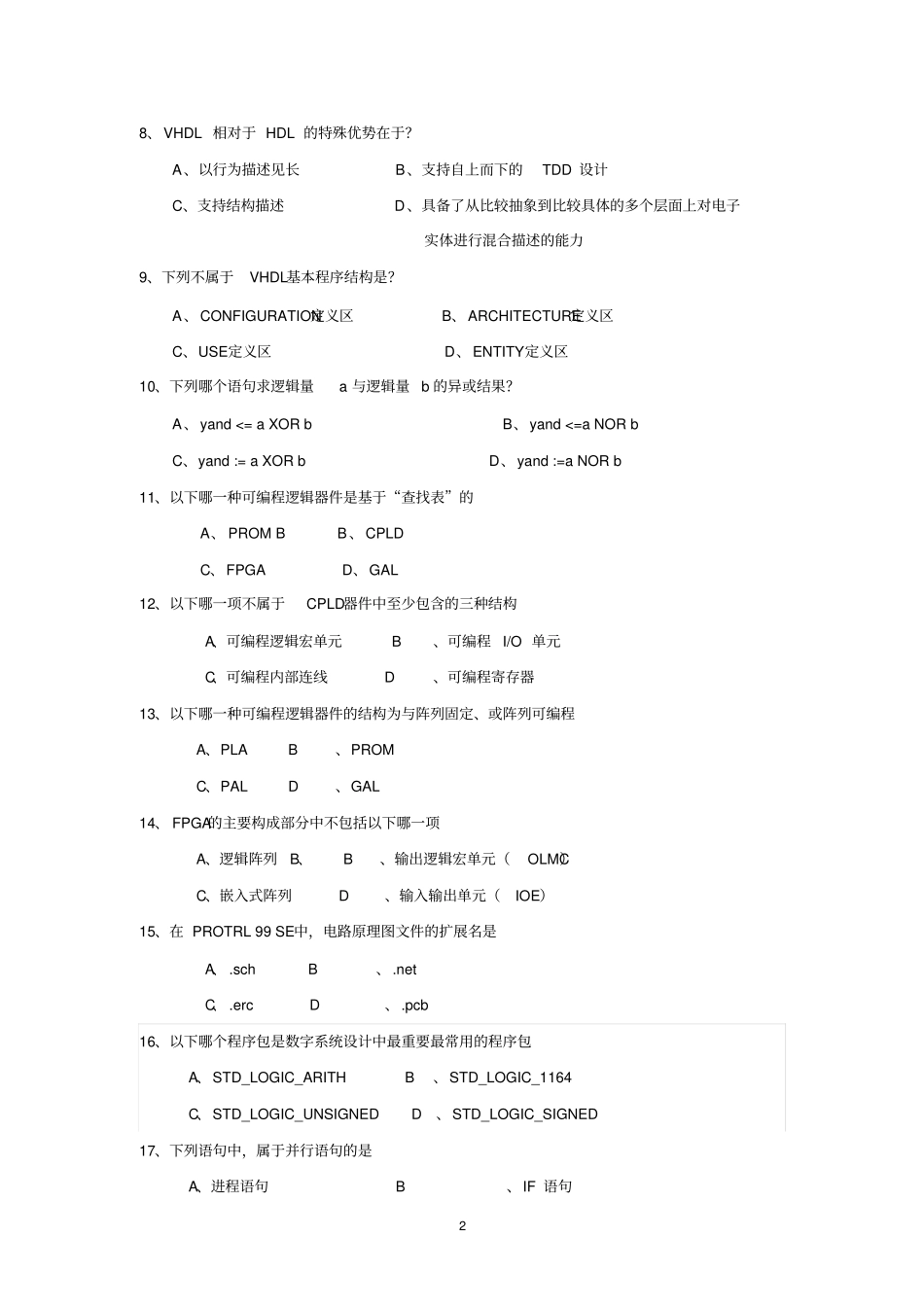

CONVERT_INTEGER() 5、该程序实现的功能是()A

s=abc+ac+bc B

s=abc+ac+bc C

s=abc+ac+bc D

s=ac+bc 6、以下哪个文件扩展名是仿真波形的文件扩展名

A、vhd B、vwf C、 bdf D、sof 7、以下哪种定义代表向量定义

A 、a IN STD_LOGIC B、a OUT STD_LOGIC_VECTOR(3 DOWNTO 0) C、a OUT INTEGER RANGE 0 to 300 D、a BUFFER BOOLEAN 图 1 2 8、VHDL 相对于 HDL 的特殊优势在于

A、以行为描述见长B、支持自上而下的TDD 设计C、支持结构描述D、具备了从比较抽象到比较具体的多个层面上对电子实体进行混合描述的能力9、下列不属于VHDL基本程序结构是

A、CONFIGURATION定义区B、ARCHITECTURE定