射频电路印制板(PCB)抗电磁干扰(EMI)设计减小字体 增大字体 作者:佚名 来源:本站整理 发布时间:2010-04-02 12:29:43摘要:为保证电路性能,在进行射频电路印制电路板( PCB)设计时应考虑 EMC 性,这对于减小系统电磁信息辐射具有重要的意义

文中重点讨论按元器件的布局和布线原则来最大限度地实现电路的性能指标,达到抗干扰的设计目的

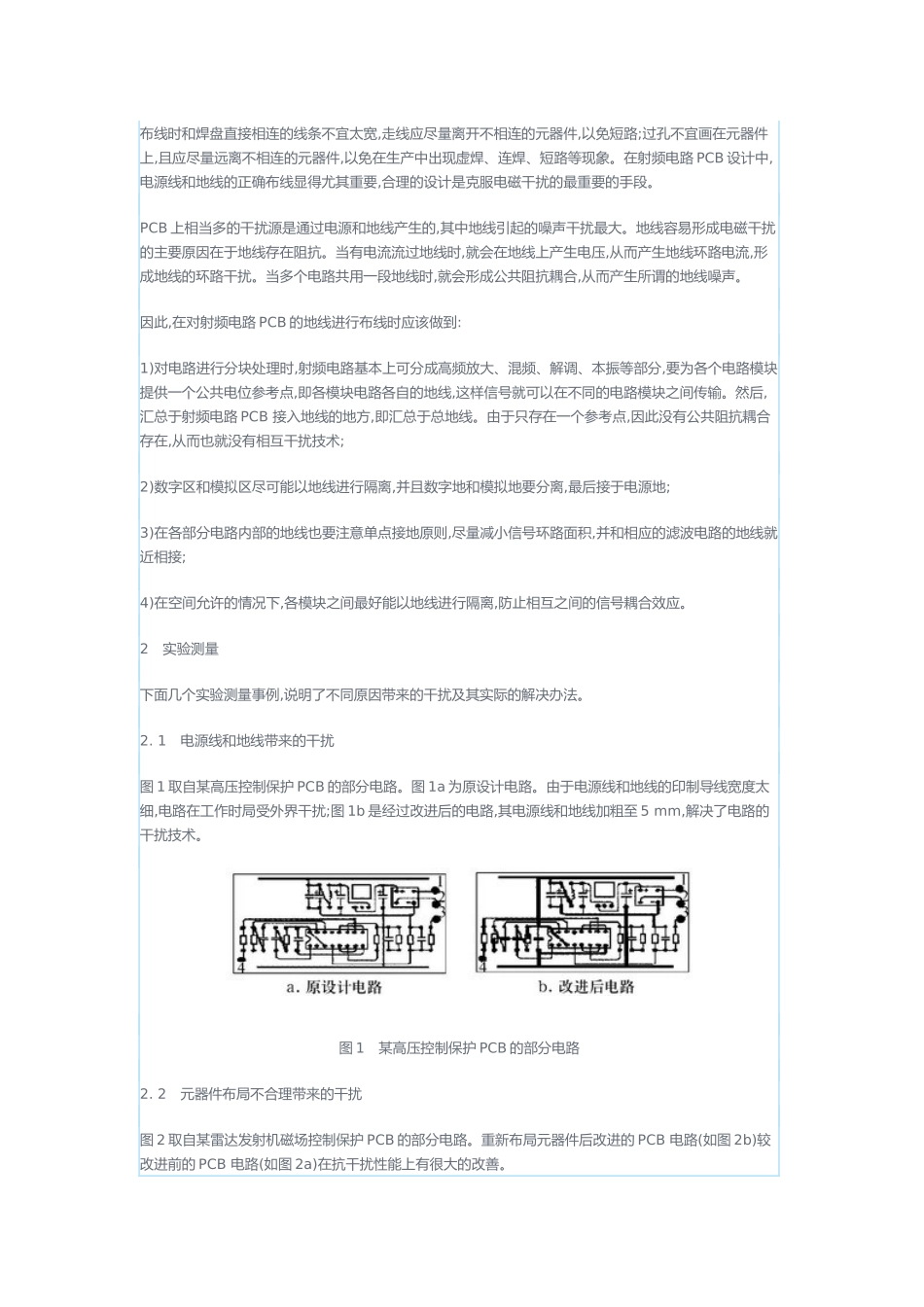

通过几个实验测量事例,分析了干扰印制板抗干扰性能的几个不同因素,说明了印制板制作过程中应采取的实际的解决办法

引 言 随着通信技术的趋势,无线射频电路技术运用越来越广,其中的射频电路的性能指标直接干扰整个产品的质量,射频电路印制电路板( PCB)的抗干扰设计对于减小系统电磁信息辐射具有重要的意义

射频电路 PCB的密度越来越高, PCB 设计的好坏对抗干扰能力干扰很大,同一电路,不同的 PCB 设计结构,其性能指标会相差很大

电磁干扰信号如果处理不当,可能造成整个电路系统的无法正常工作,因此怎么防止和抑制电磁干扰,提高 EMC 性,就成为设计射频电路 PCB 时的一个非常重要的课题

EMC 性 EMC 是指电子系统在规定的电磁环境中按照设计规则能正常工作的能力

电子系统所受的电磁干扰不仅来自电场和磁场的辐射,也有线路公共阻抗、导线间耦合和电路结构的干扰

在研制设计电路时,希望设计的印制电路板尽可能不易受外界干扰的干扰,而且也尽可能小地干扰干扰别的电子系统

设计印制板首要的任务是对电路进行分析,确定关键电路

这就是要识别哪些电路是干扰源,哪些电路是敏感电路,弄清干扰源可能通过什么路径干扰敏感电路

射频电路工作频率高,干扰源主要是通过电磁辐射来干扰敏感电路,因此射频电路 PCB 板抗干扰设计的目的是减小 PCB 板的电磁辐射和 PCB 板上电路之间的串扰

1 射频电路板设计 1

1 元器件的布局 由于 SMT 一般采