毕业设计外文资料翻译学院:信息科学与工程学院专业:电子科学与技术姓名:康兴华学号:040704128 外文出处:填入英文资料名称附件: 1

外文资料翻译译文;2

指导教师评语:签名:年月日( 用外文写 ) 附件 1:外文资料翻译译文UART的核核的概况带有 Avalon 接口的通用异步接收 /发送器的核( UART 的核)所执行的方式是为了沟通一个系统内置的Altera FPGA 和外部设备之间的串行字符流

核实行RS-232 协议计时,并提供可调波特率,奇偶,停止和数据位,以及可选RTS/CTS 的流量控制信号

它的功能设置是可配置的,对于给定的系统,它允许设计者实现必要的功能

核提供了一个简单的寄存器映射的Avalon 存储器映射( Avalon-MM )的从属接口,使 Avalon-MM 的主控外设(如一个NiosII 处理器)通过读和写控制寄存器和数据寄存器来简单的与核沟通

该 UART 的核是 SOPC Builder-ready,并且可以轻松的集成到任何SOPC Builder 产生的系统中,本章包含以下章节:■“功能描述”见 8-2 页■“设备和工具支持”见8-4 页■“在 SOPC Builder 中对核实例化”见8-4 页■“硬件仿真考虑”见8-9 页■“软件编程模型”见8-9 页1

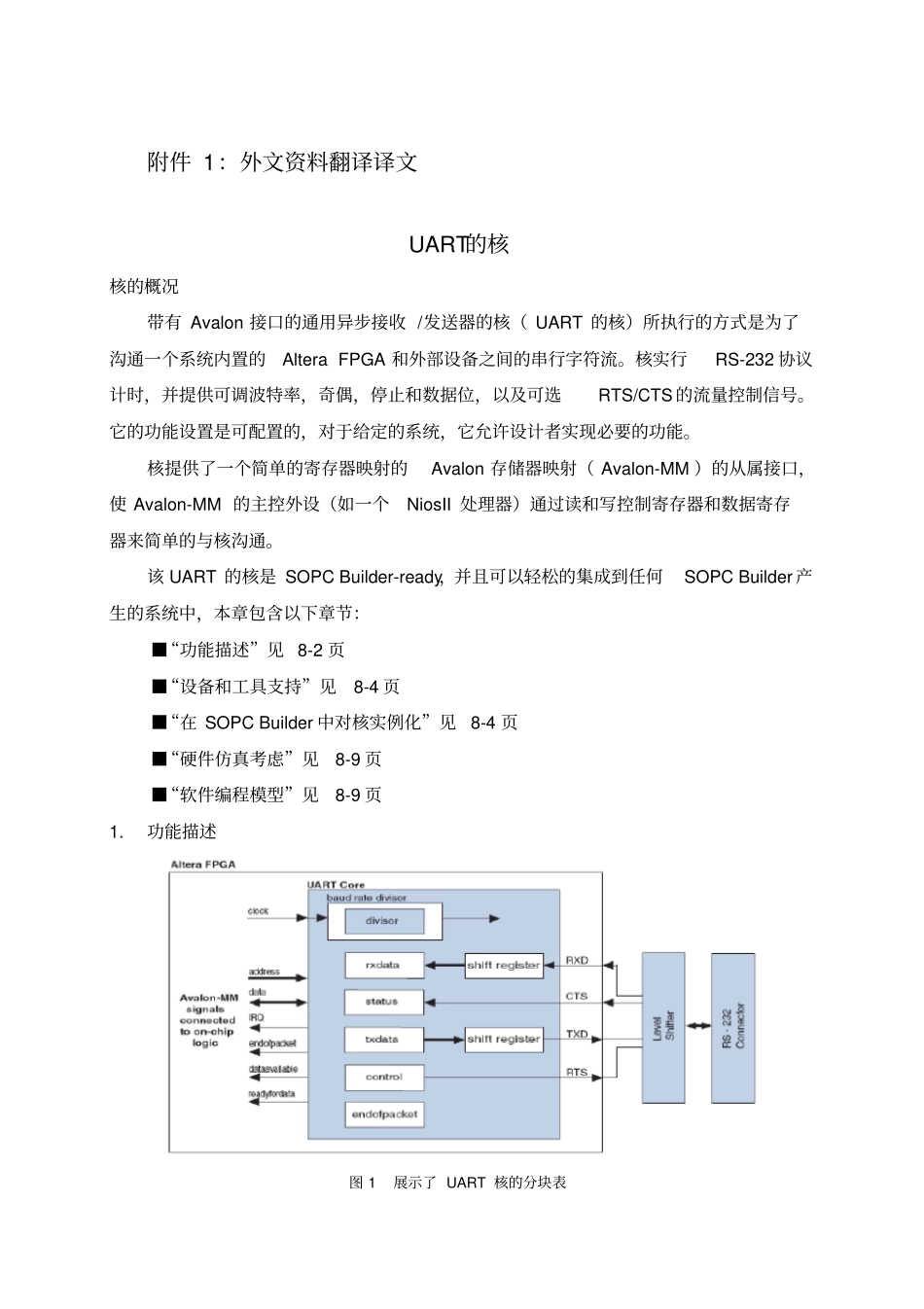

功能描述图 1 展示了 UART 核的分块表核有两个用户可见部分:■寄存器文件,它通过Avalon-MM 从属端口来存取■RS-232 的信号, RXD,TXD ,CTS 和 RTS 1

1 Avalon-MM从属接口和寄存器该 UART 的核提供了一个 Avalon-MM 从属接口到内部寄存器文件

连接用户接口包含 6 个 16 位的寄存器:控制,状态,rxdata,txdata,除数, endofpacket

一个主控外设,如一个 NiosII 处理器,可以