电子设计自动化实验报告姓名:路传涛学号: 201215728 时间11-12 第四大节地点 S-5B208 七段数码显示译码器设计1

实验目的:学习 7 段数码显示译码器设计,学习VHDL的多层次设计方法

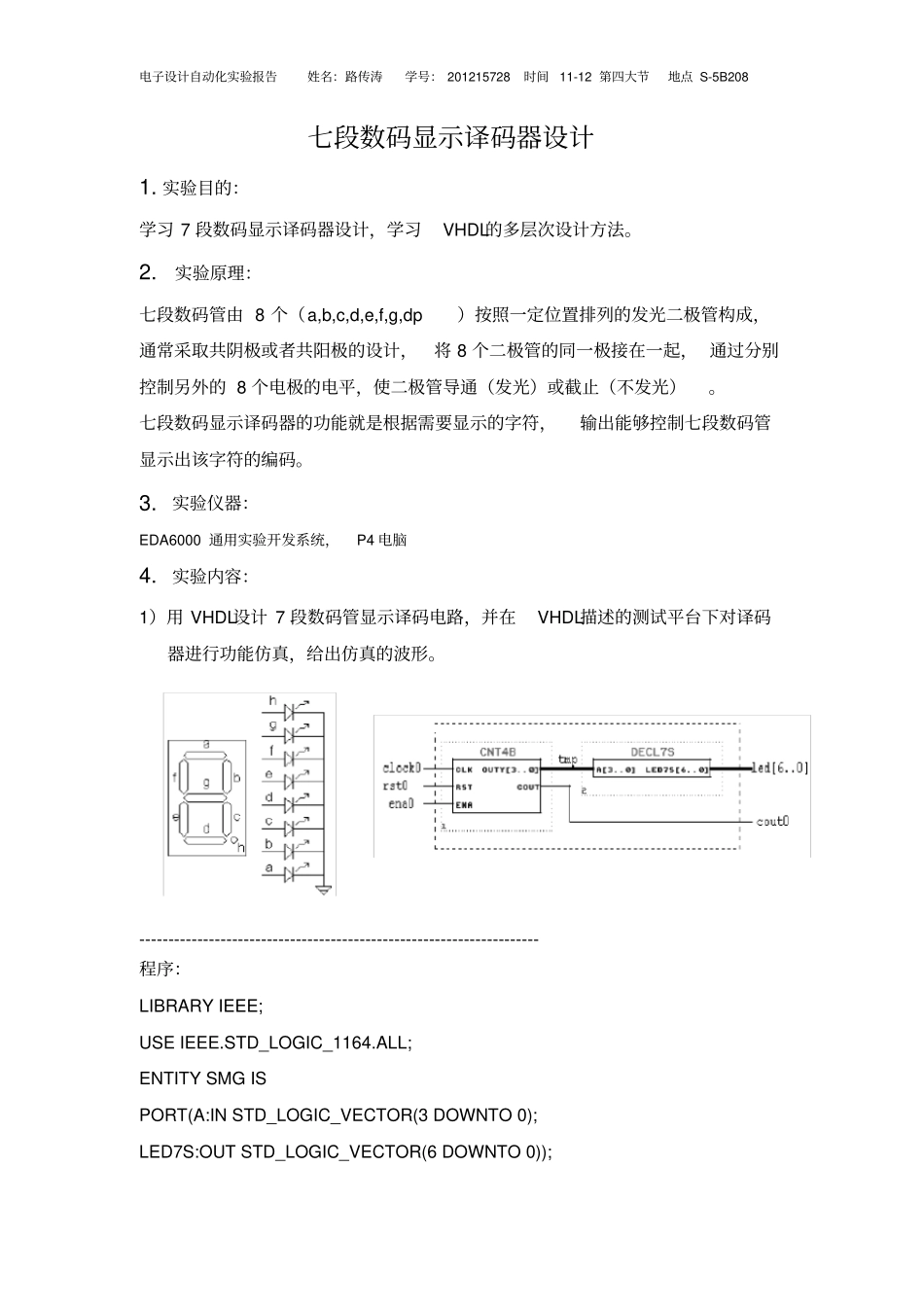

实验原理:七段数码管由 8 个(a,b,c,d,e,f,g,dp)按照一定位置排列的发光二极管构成,通常采取共阴极或者共阳极的设计,将 8 个二极管的同一极接在一起, 通过分别控制另外的 8 个电极的电平,使二极管导通(发光)或截止(不发光)

七段数码显示译码器的功能就是根据需要显示的字符,输出能够控制七段数码管显示出该字符的编码

实验仪器:EDA6000 通用实验开发系统,P4 电脑4

实验内容:1)用 VHDL设计 7 段数码管显示译码电路,并在VHDL描述的测试平台下对译码器进行功能仿真,给出仿真的波形

---------------------------------------------------------------------程序:LIBRARY IEEE; USE IEEE

STD_LOGIC_1164

ALL; ENTITY SMG IS PORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); 电子设计自动化实验报告姓名:路传涛学号: 201215728 时间11-12 第四大节地点 S-5B208 END; ARCHITECTURE ONE OF SMG IS BEGIN PROCESS(A) BEGIN CASE A IS WHEN"0000"=>LED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SLED7SNULL; END CAS