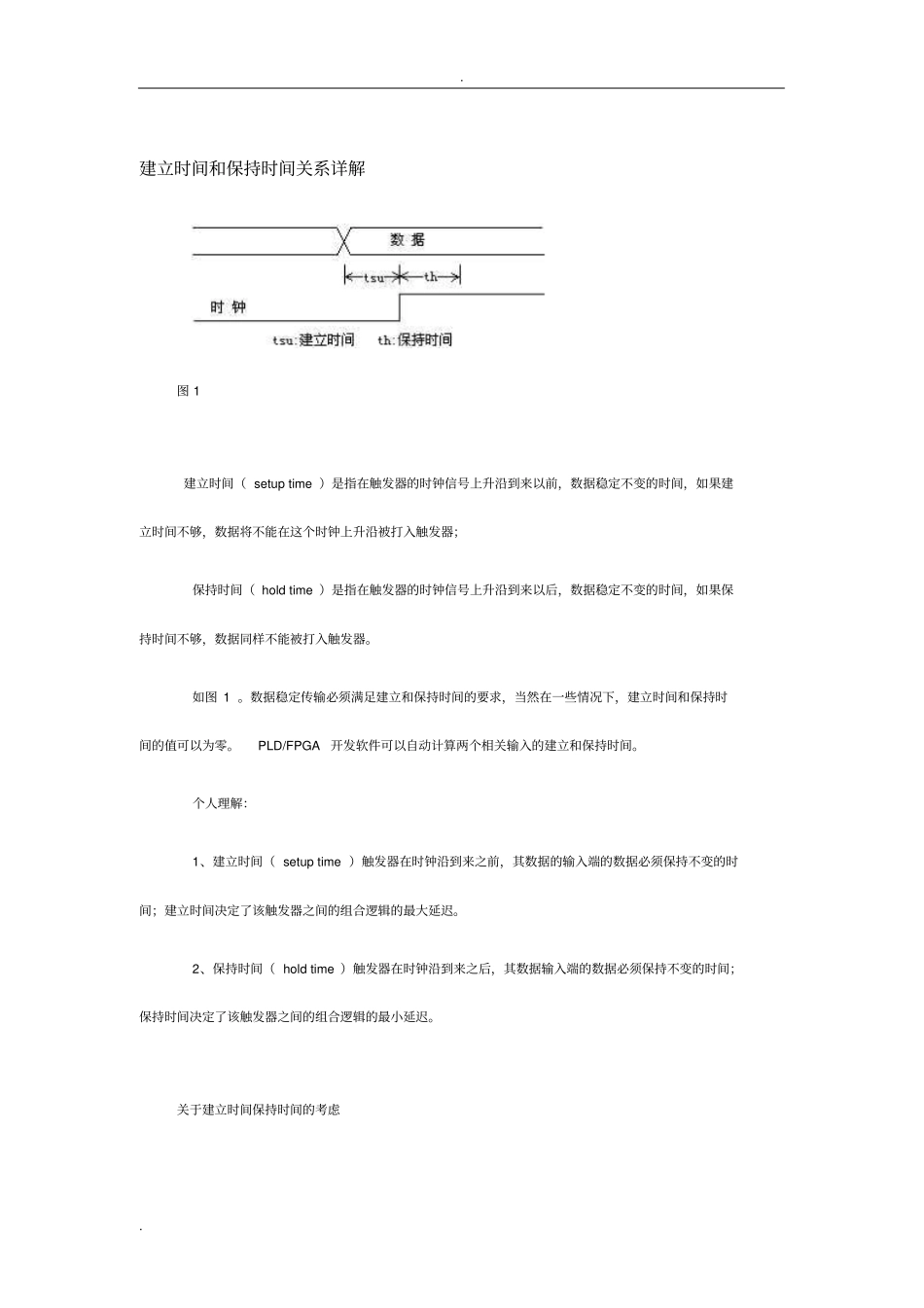

建立时间和保持时间关系详解图 1 建立时间( setup time )是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间( hold time )是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零

PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间

个人理解:1、建立时间( setup time )触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟

2、保持时间( hold time )触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟

关于建立时间保持时间的考虑

华为题目: 时钟周期为T ,触发器 D1 的建立时间最大为T1max ,最小为 T1min

组合逻辑电路最大延迟为 T2max ,最小为 T2min

问:触发器D2 的建立时间T3 和保持时间T4 应满足什么条件

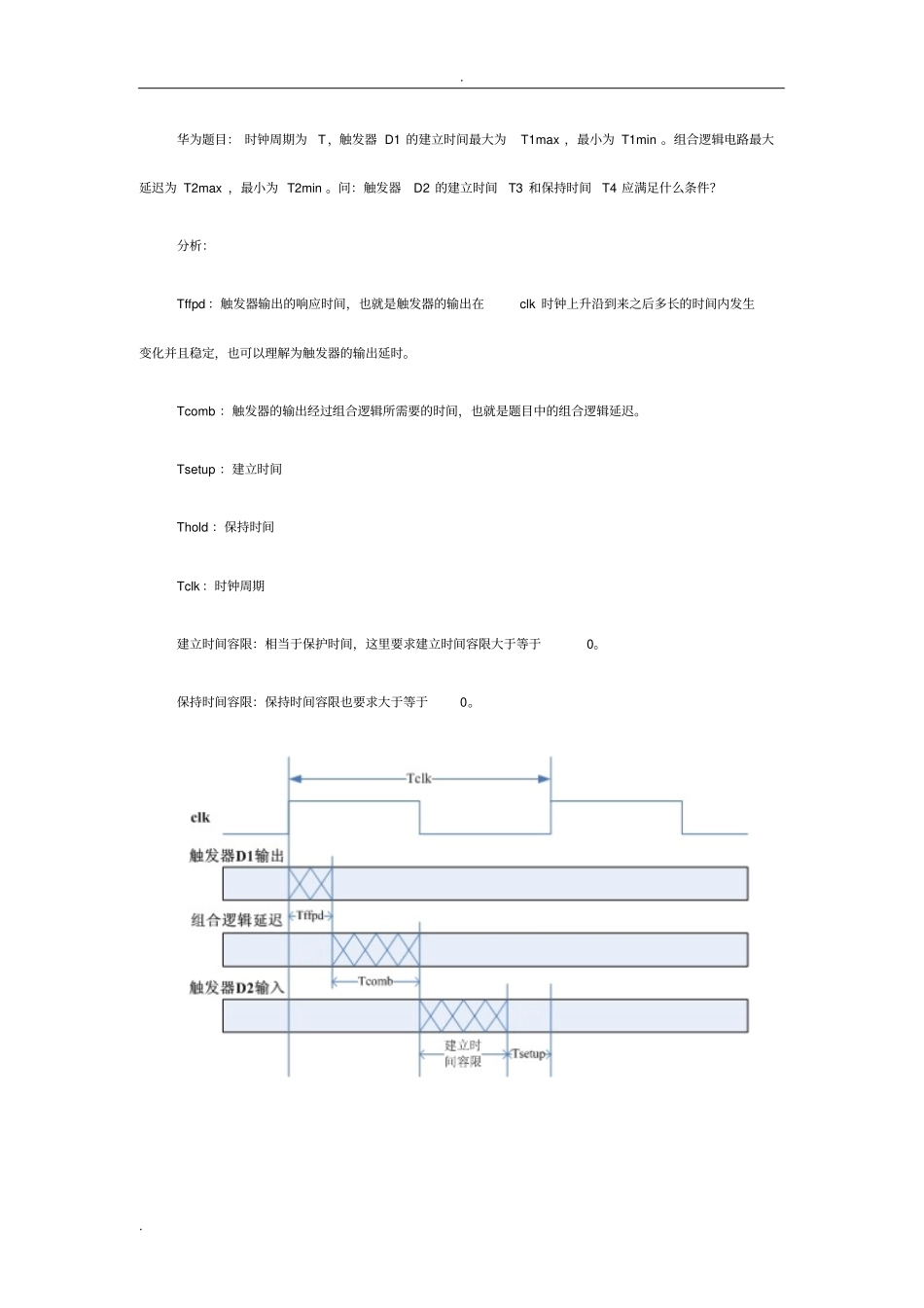

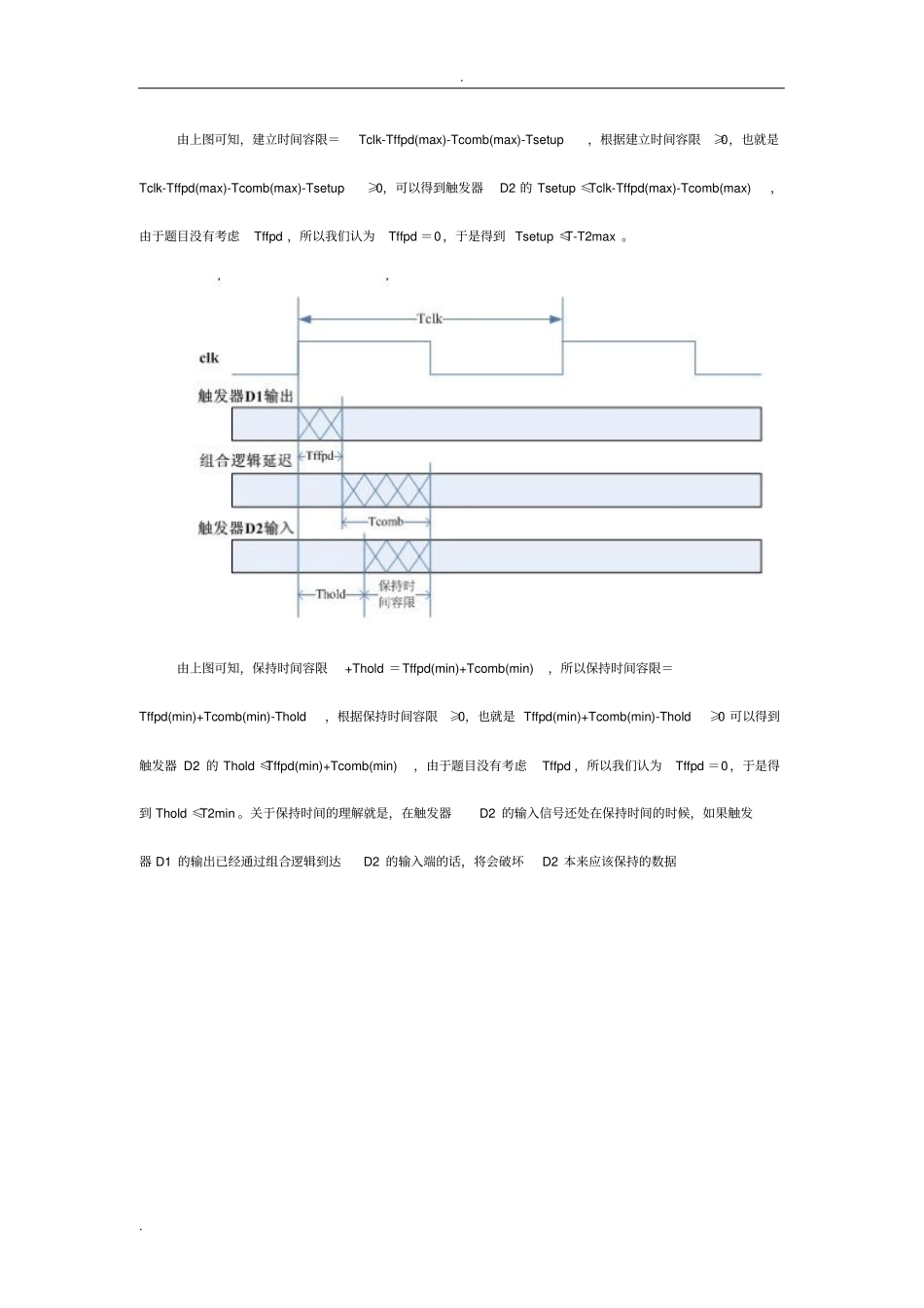

分析:Tffpd :触发器输出的响应时间,也就是触发器的输出在clk 时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时

Tcomb :触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟

Tsetup :建立时间Thold :保持时间Tclk :时钟周期建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0

保持时间容限:保持时间容限也要求大于等于0

由上图可知,建立时间容限=Tclk-Tffpd(max)-Tcomb(max)-Tsetup,根据建立时间容限≥0,也就是Tclk