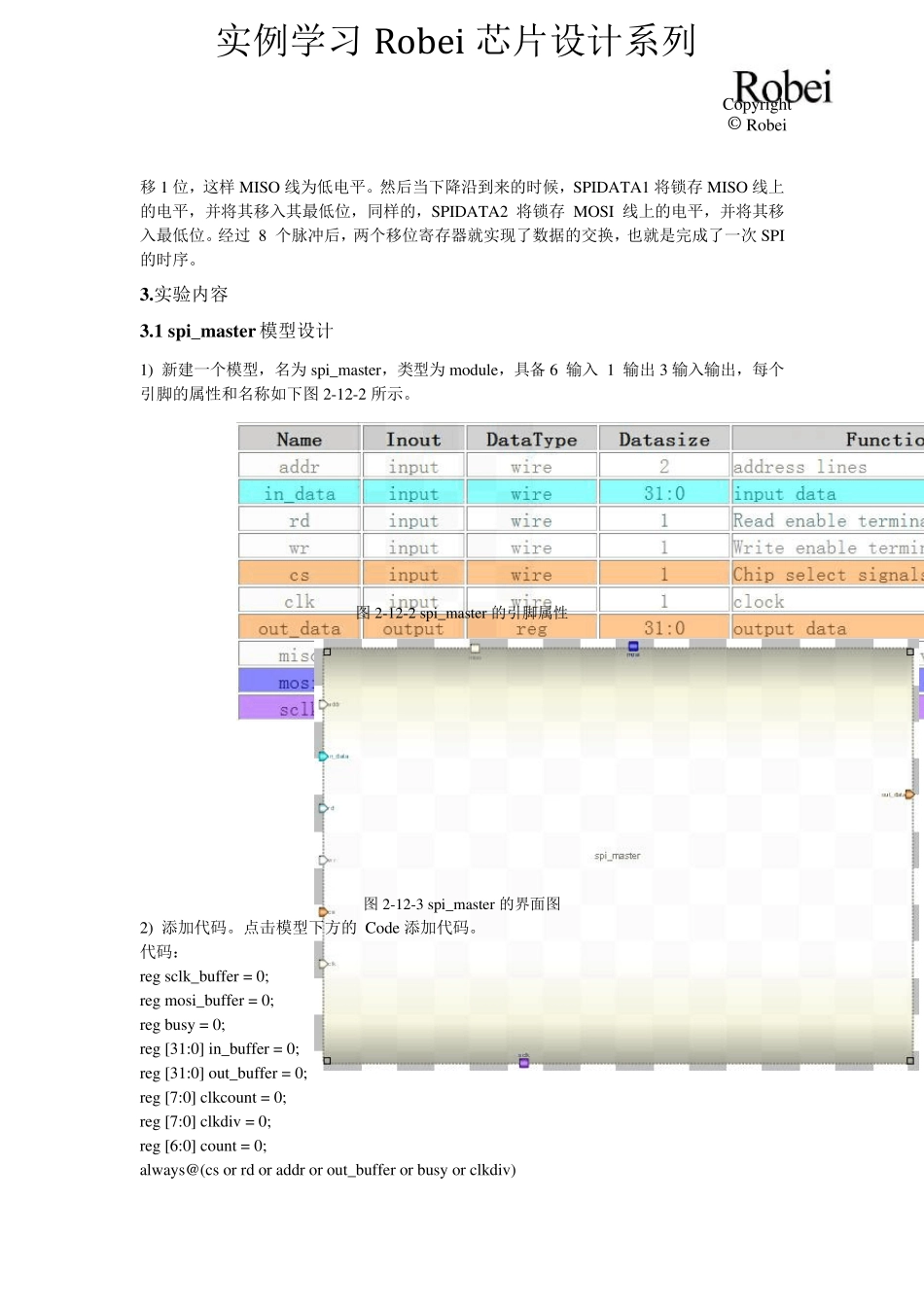

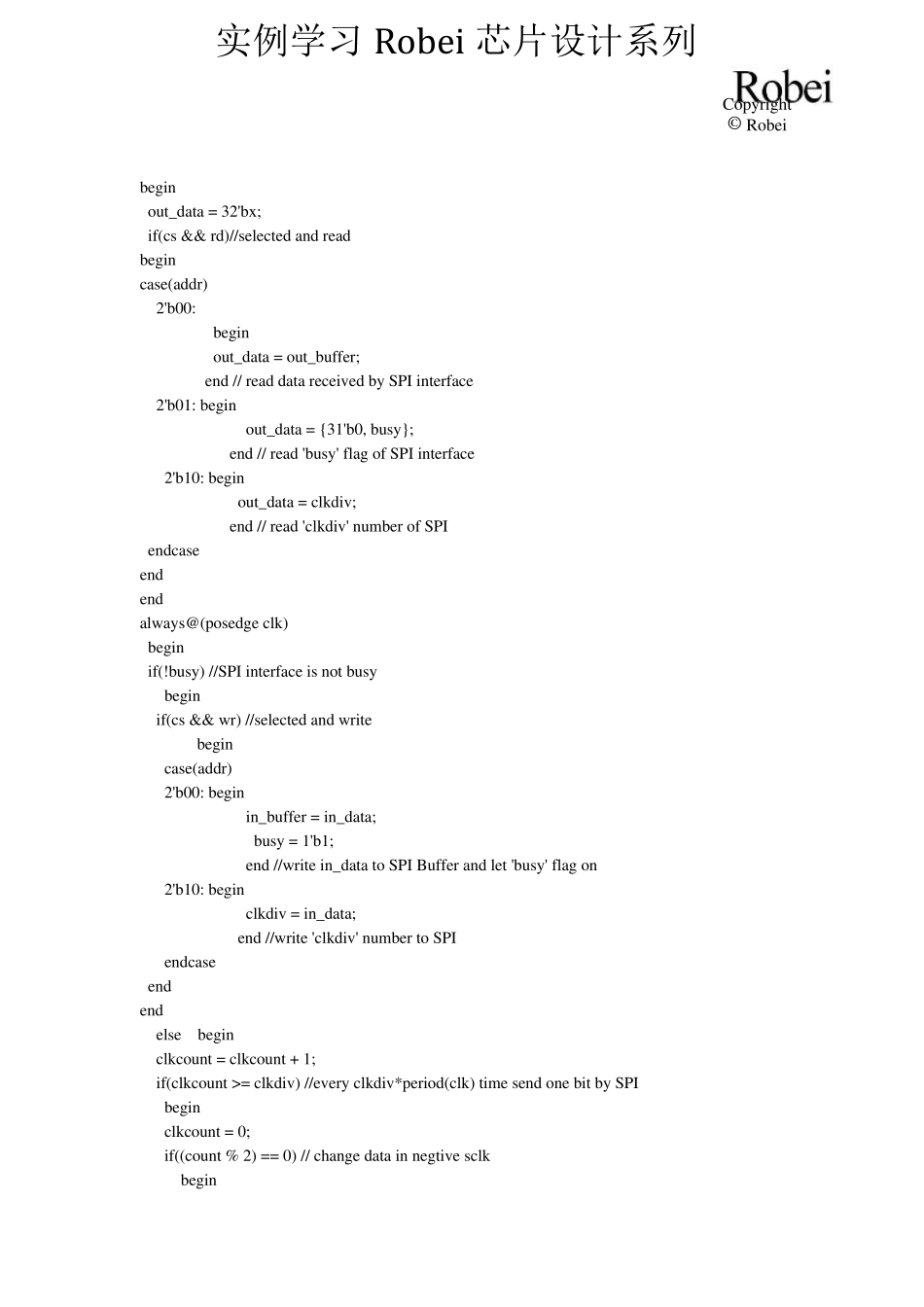

实例学习Ro bei 芯片设计系列 Copyright © Robei 十二SPI 总线接口的verilog 的实现 1

实验目的 项目中使用的许多器件需要SPI 接口进行配置,比如PLL:ADF4350,AD:AD9627,VGA:AD8372 等,本实验根据SPI 协议,编写了一个简单的SPI 读写程序,可以进行32位数据的读写,可以设置SPI SCLK 相对于主时钟的分频比

实验原理 SPI 总线系统是一种同步串行外设接口,它可以使MCU 与各种外围设备以串行方式进行通信以交换信息

外围设置FLASHRAM、网络控制器、LCD 显示驱动器、A/D 转换器和MCU 等

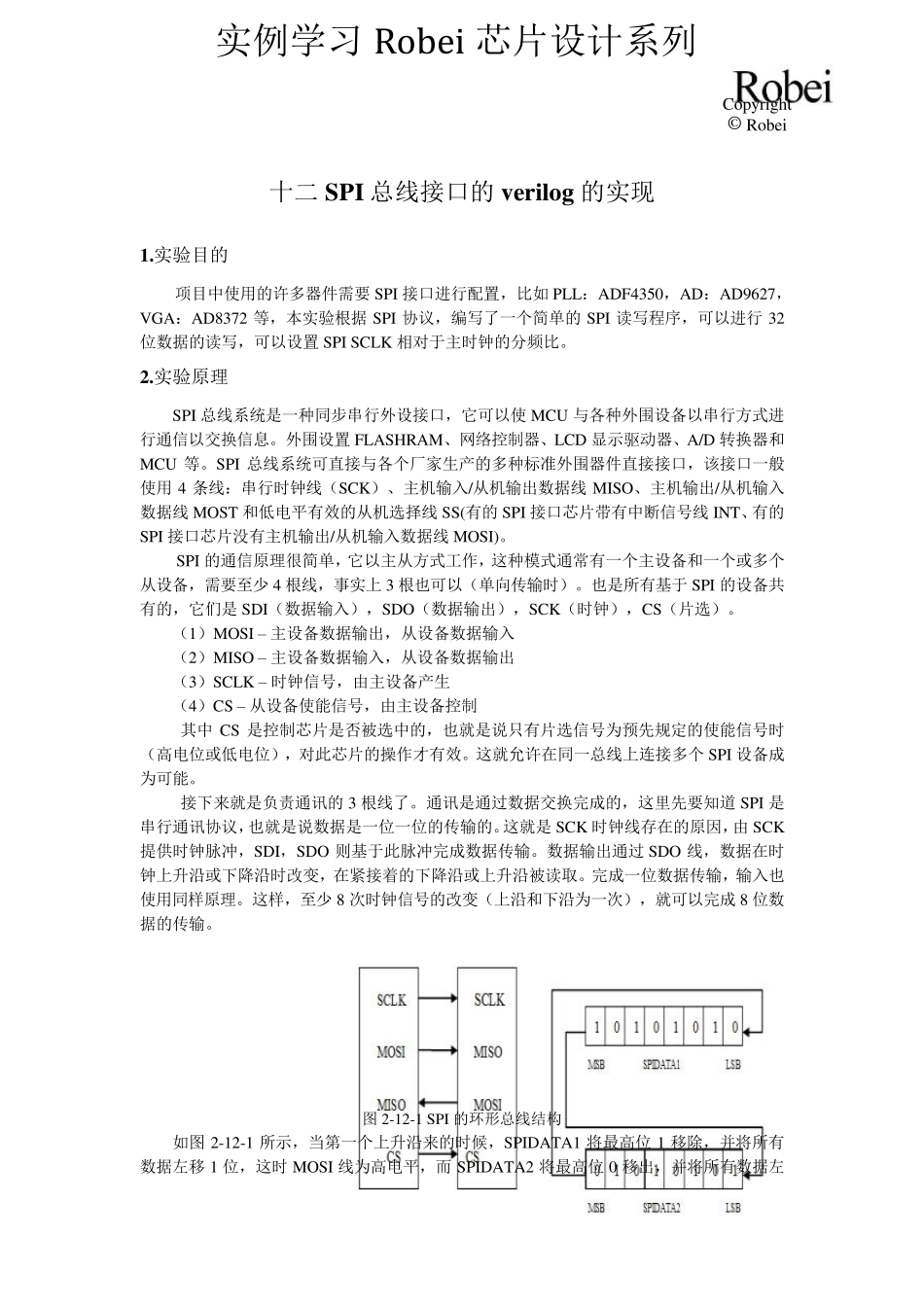

SPI 总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4 条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST 和低电平有效的从机选择线SS(有的SPI 接口芯片带有中断信号线INT、有的SPI 接口芯片没有主机输出/从机输入数据线MOSI)

SPI 的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4 根线,事实上3 根也可以(单向传输时)

也是所有基于SPI 的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)

(1)MOSI – 主设备数据输出,从设备数据输入 (2)MISO – 主设备数据输入,从设备数据输出 (3)SCLK – 时钟信号,由主设备产生 (4)CS – 从设备使能信号,由主设备控制 其中CS 是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操 作才 有效

这就允 许在 同一总线上连 接多个SPI 设备成为可能

接下 来 就是负 责 通讯 的3 根线了

通讯 是通过 数据交换完 成 的,