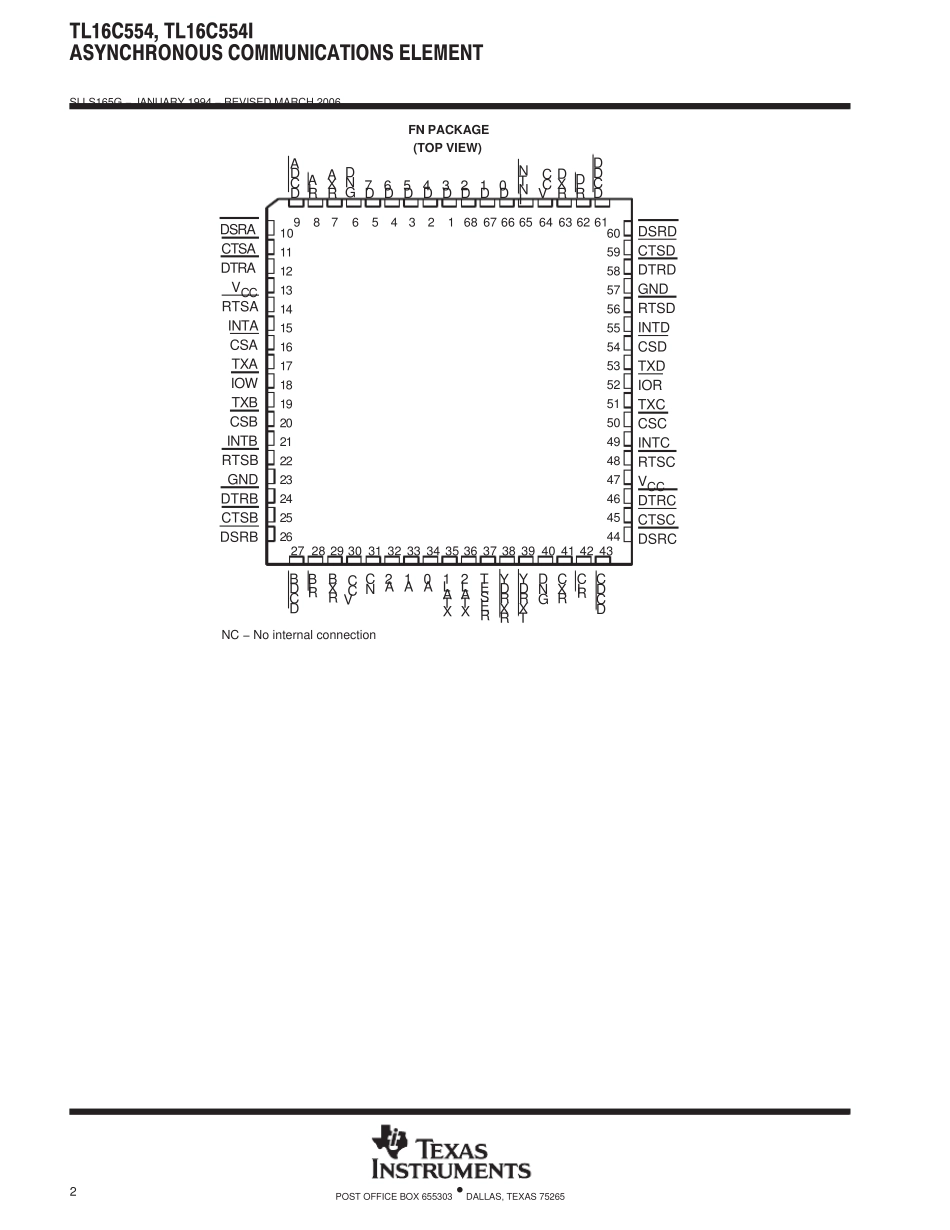

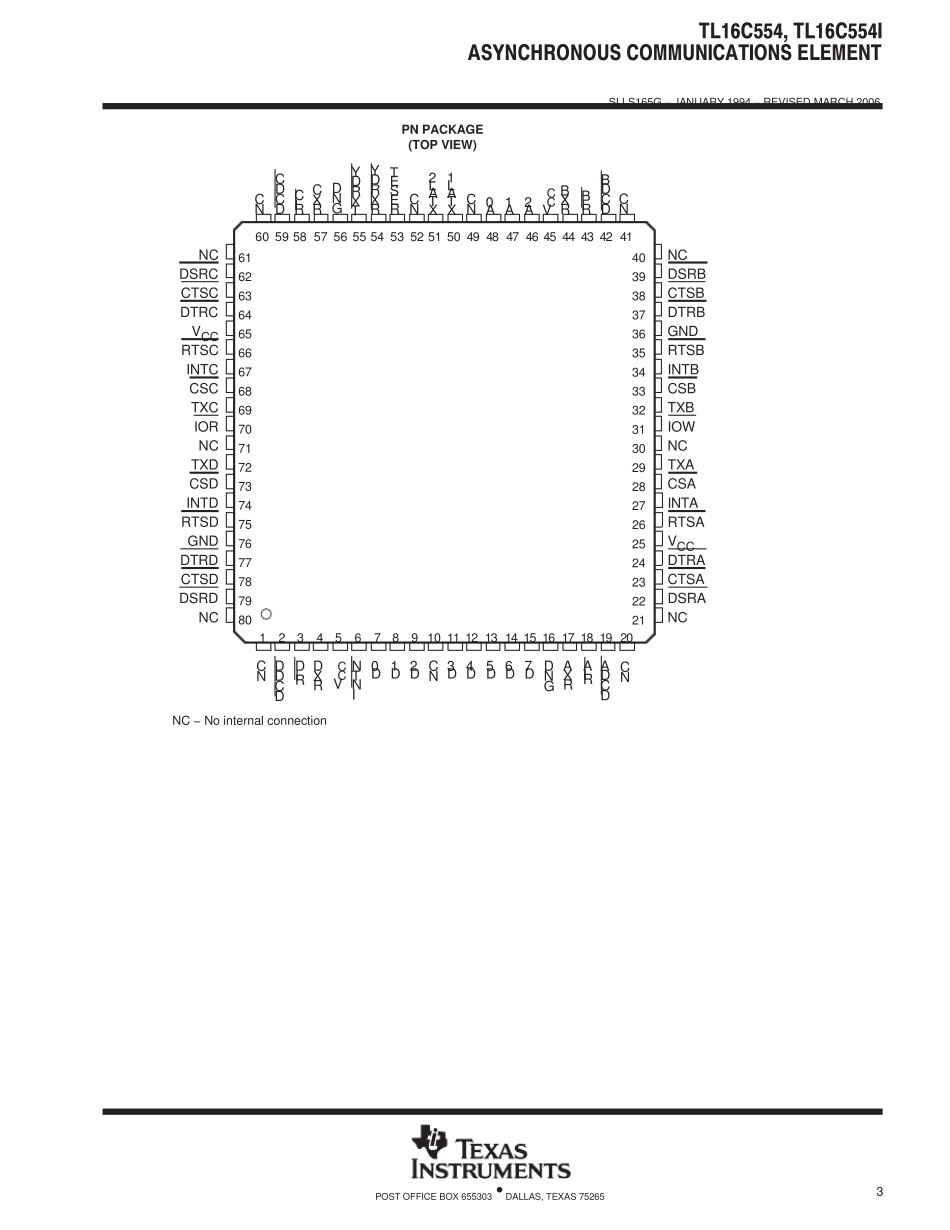

TL16C554, TL16C554IASYNCHRONOUS COMMUNICATIONS ELEMENTąąSLLS165G − JANUARY 1994 − REVISED MARCH 20061POST OFFICE BOX 655303 • DALLAS, TEXAS 75265DIntegrated Asynchronous CommunicationsElementDConsists of Four Improved TL16C550 ACEsPlus Steering LogicDIn FIFO Mode, Each ACE Transmitter andReceiver Is Buffered With 16-Byte FIFO toReduce the Number of Interrupts to CPUDIn TL16C450 Mode, Hold and ShiftRegisters Eliminate Need for PreciseSynchronization Between the CPU andSerial DataDUp to 16-MHz Clock Rate for up to 1-MbaudOperationDProgrammable Baud Rate GeneratorsWhich Allow Division of Any InputReference Clock by 1 to (216− 1) andGenerate an Internal 16 × ClockDAdds or Deletes Standard AsynchronousCommunication Bits (Start, Stop, andParity) to or From the Serial Data StreamDIndependently Controlled Transmit,Receive, Line Status, and Data SetInterruptsDFully Programmable Serial InterfaceCharacteristics:− 5-, 6-, 7-, or 8-Bit Characters− Even-, Odd-, or No-Parity Bit− 1-, 1 1/2-, or 2-Stop Bit Generation− Baud Generation (DC to 1-Mbit PerSecond)DFalse Start Bit DetectionDComplete Status Reporting CapabilitiesDLine Break Generation and DetectionDInternal Diagnostic Capabilities:− Loopback Controls for CommunicationsLink Fault Isolation− Break, Parity, Overrun, Framing ErrorSimulationDFully Prioritized Interrupt System ControlsDModem Control Functions (CTS, RTS, DSR,DTR, RI, and DCD)D3-State Outputs Provide TTL DriveCapabilities for Bidirectional Data Bus andControl Bus descriptionThe TL16C554 and the TL16C554I are enhanced quadruple versions of the TL16C550B asynchronouscommunications element (ACE). Each channel performs serial-to-parallel conversion on data charactersreceived from peripheral devices or modems and parallel-to-serial conversion on...