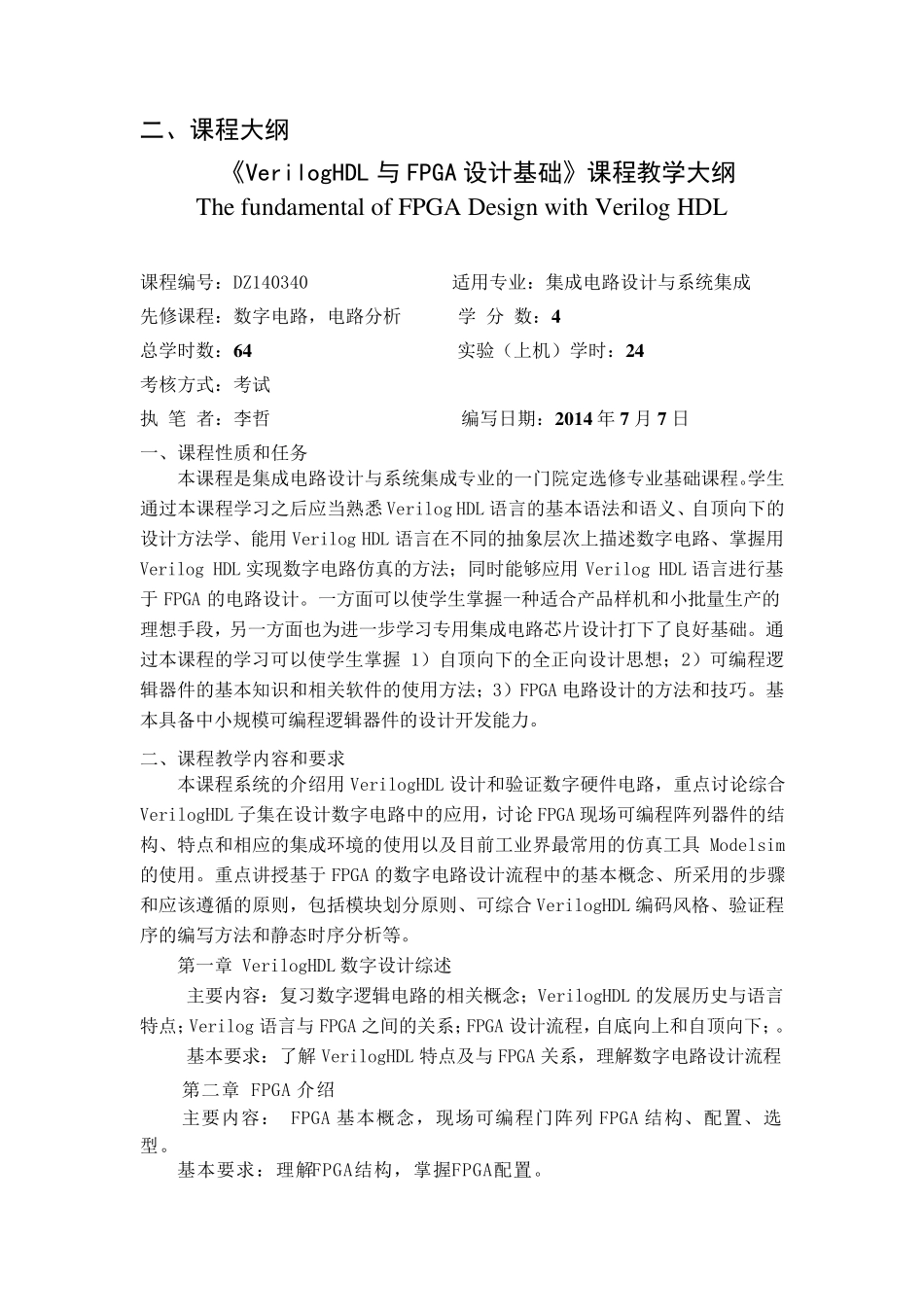

西 安 邮 电 大 学 课 程 教 案 课 程 名 称 : VerilogHDL 与 FPGA 设计基础 授课 教 师: ** 授课 教 师所在学 院: 电 子工程 学 院 授课 班级: 电 路 1201~02 授课 学 期: 2014-2015-01 学 期 一、基本信息 课程名称 VerilogHDL 与 FPGA 设计基础 课程性质 ○必修 ⊙限选 ○选修 ○素拓 ○跨学科 授课专业班级 学生人数: 67 所处年级 ○ 一年级 ○ 二年级 ⊙ 三年级 ○ 四年级 总学时 64 理论课时 40 实验课时 24 学分 4 课程教材 VerilogHDL 与 FPGA 设计基础 上课时间 2014-2015-1 上课地点 A337、A322 答疑时间 答疑地点 2#112 先修课程 本课程在授课对象所学专业人才培养中的作用与地位 本课程是集成电路设计与系统集成专业的一门专业基础课程,学生在先修课程数字电路基础上,掌握使用 VerilogHDL 进行数字电路设计、仿真,并在 Fpga 器件上实现数字逻辑

初步掌握集成电路和数字系统的设计方法,培养学生从事集成电路设计技能,对学生进入集成电路设计领域有很重要作用

本课程在知识传授、能力提升、素质培养各方面的教学目标 掌握基于 FPGAVerilog HDL 实现数字电路仿真的方法

一方面可以使学生掌握一种适合产品样机和小批量生产的理想手段,另一方面也为进一步学习专用集成电路芯片设计打下了良好基础

通过本课程的学习可以使学生掌握 1)自顶向下的全正向设计思想;2)可编程逻辑器件的基本知识和相关软件的使用方法;3)FPGA 电路设计的方法和技巧

基本具备 中小规 模 可编程逻辑器件的设计开 发 能力

学生情 况 分析 注 :本栏 目建 议 各位老 师 通过与学生深 入沟 通、向前 续 课程授课教师 和辅 导 员 老 师 了解 情