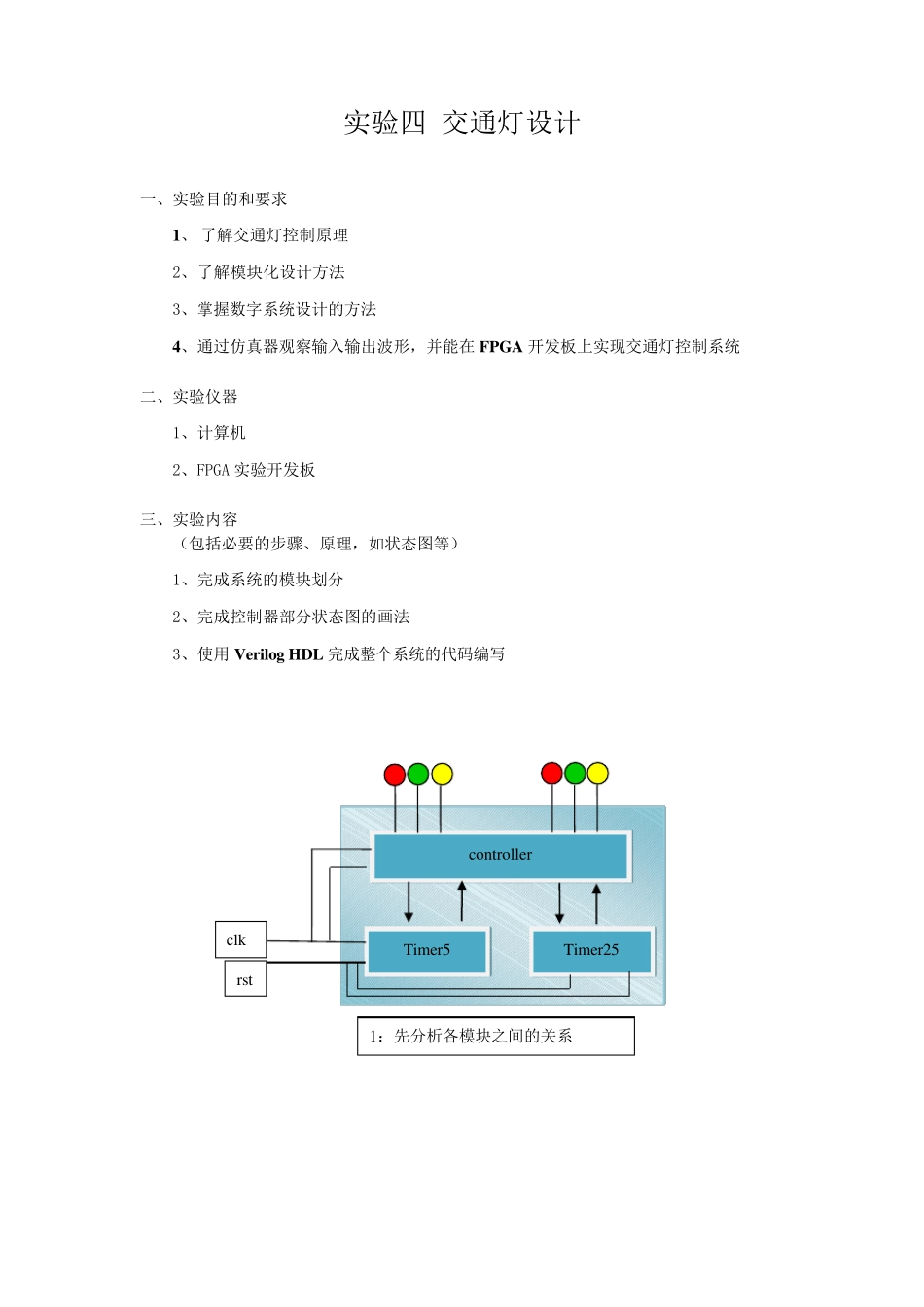

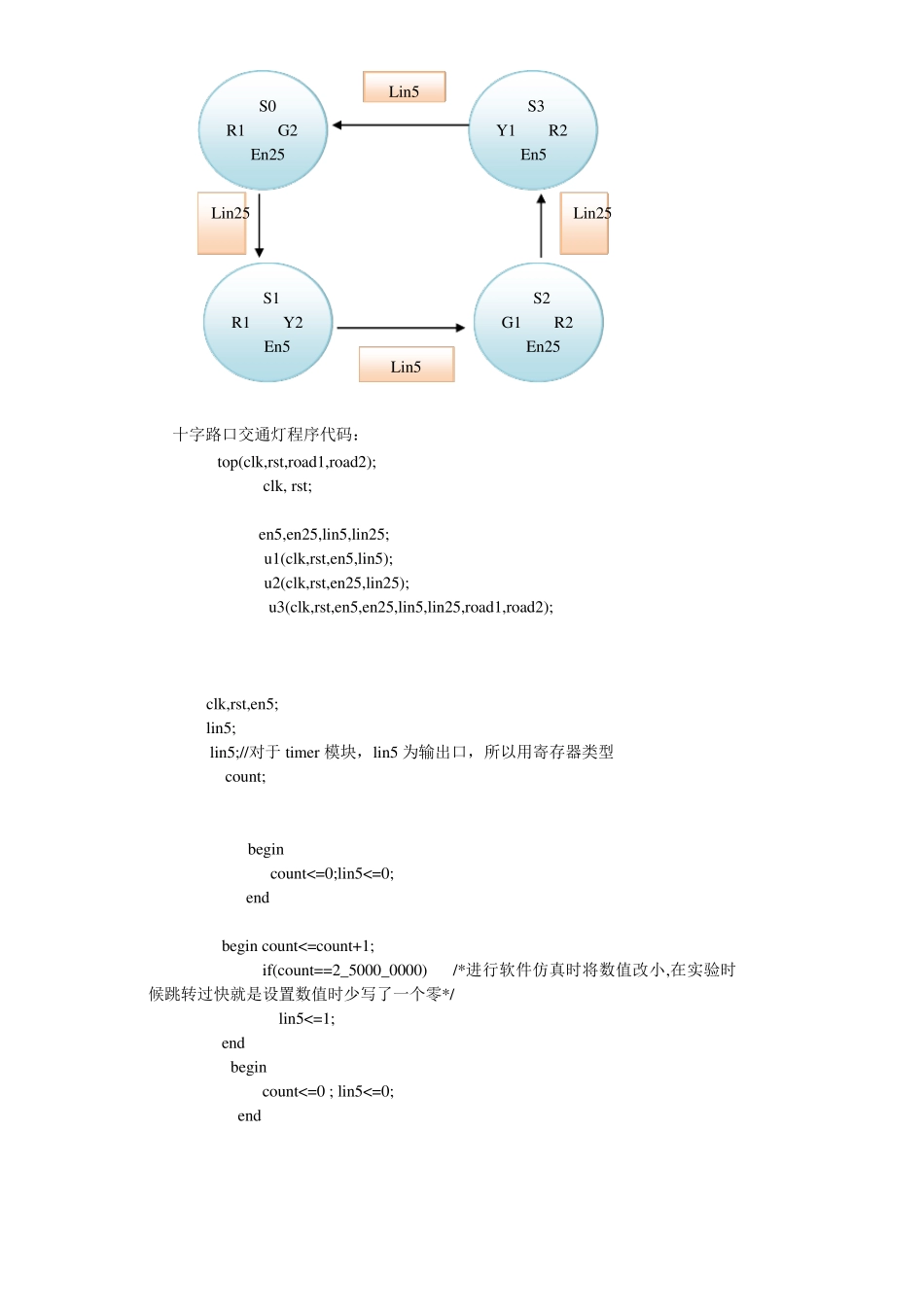

实验四 交通灯设计 一、实验目的和要求 1、 了解交通灯控制原理 2、了解模块化设计方法 3、掌握数字系统设计的方法 4、通过仿真器观察输入输出波形,并能在 FPGA 开发板上实现交通灯控制系统 二、实验仪器 1、计算机 2、FPGA 实验开发板 三、实验内容 (包括必要的步骤、原理,如状态图等) 1、完成系统的模块划分 2、完成控制器部分状态图的画法 3、使用 Verilog HDL 完成整个系统的代码编写 1:先分析各模块之间的关系 controller Timer5 Timer25 rst clk 十字路口交通灯程序代码: top(clk,rst,road1,road2); clk, rst; en5,en25,lin5,lin25; u1(clk,rst,en5,lin5); u2(clk,rst,en25,lin25); u3(clk,rst,en5,en25,lin5,lin25,road1,road2); clk,rst,en5; lin5; lin5;//对于timer 模块,lin5 为输出口,所以用寄存器类型 count; begin count