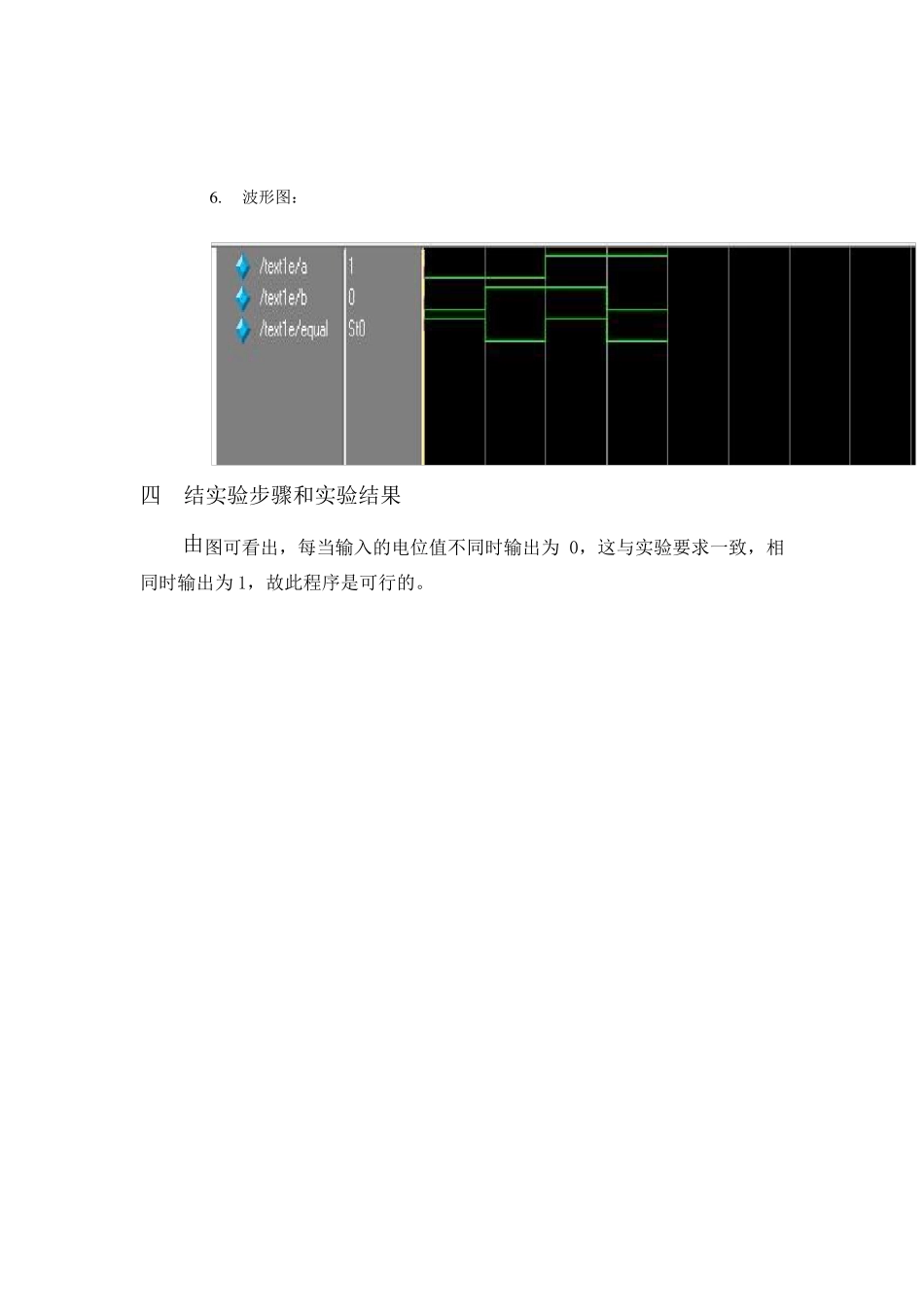

实验一 简单组合逻辑电路的设计 一 实验要求 1. 用verilog HDL语言描写出简单的一位数据比较器及其测试程序; 2. 用测试程序对比较器进行波形仿真测试;画出仿真波形; 3. 总结实验步骤和实验结果。 二 实验原理与内容 4. 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL 中 , 描述 组合逻辑时 常 使 用assign结构 。 注 意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 5. 模块源代码 测试模块: 6 . 波形图: 四 结实验步骤和实验结果 由图可看出,每当输入的电位值不同时输出为0,这与实验要求一致,相同时输出为1,故此程序是可行的。 实验三 在verilog HDL 中使用函数 一 实验要求 1. 掌握函数在模块中的使用 2. 用测试程序进行波形仿真测试;画出仿真波形 3. 总结实验步骤和实验结果 二 实验原理与内容 与一般的程序设计语言一样;verilog HDL 也可以使用函数已是应对不同变量采取同一运算的操作。verilog HDL 函数在综合时被理解成具有独立运算功能的电路,每调用一次函数相当于改变这部分电路的输入以得到相应的计算结果。 模块源代码: module ex3(clk,n,result,reset); output[31:0] result; input[3:0] n; input reset,clk; reg[31:0] result; always @(posedge clk) begin if(!reset)result <= 0; else begin result <= n*factorial(n)/((n*2)+1); end end function[31:0] factorial; input[3:0] operand; reg[3:0] index; begin factorial = operand ? 1:0; for(index = 2;index <= operand;index = index+1) factorial = index*factorial; end endfunction endmodule `timescale 1ns/100ps `define clk_cycle 50 module ex3_t(); reg[3:0] n,i; reg reset,clk; wire[31:0] result; initial begin n=0; reset=1; clk=0; #100 reset=0; #100 reset = 1; for(i=0;i <= 15;i=i+1) begin #200 n=i; end #100 $stop; end always #`clk_cycle clk =~ clk; ex3 ex30(.clk(clk),.n(n),.result(result),.reset(reset)); always @(negedge clk) $display("at n=%d,result=%d",n,result); endmodule 波形图 : 实验四 在verilog HDL 中使用任务 一 实验要求 1. 掌握...