北京航空航天大学 2011 ~2012 学年第二学期 数字EDA 期末考试试卷 ( 2012 年 5 月 23 日) 班级:__________;学号:______________;姓名:__________________;成绩:___________ 注意事项:1 、填空题与选择题直接在试题上作答 2 、设计题在答题纸上作答 正题: 一、填空题(共 30 分,每道题 3 分) 1. 写出表达式以实现对应电路的逻辑功能

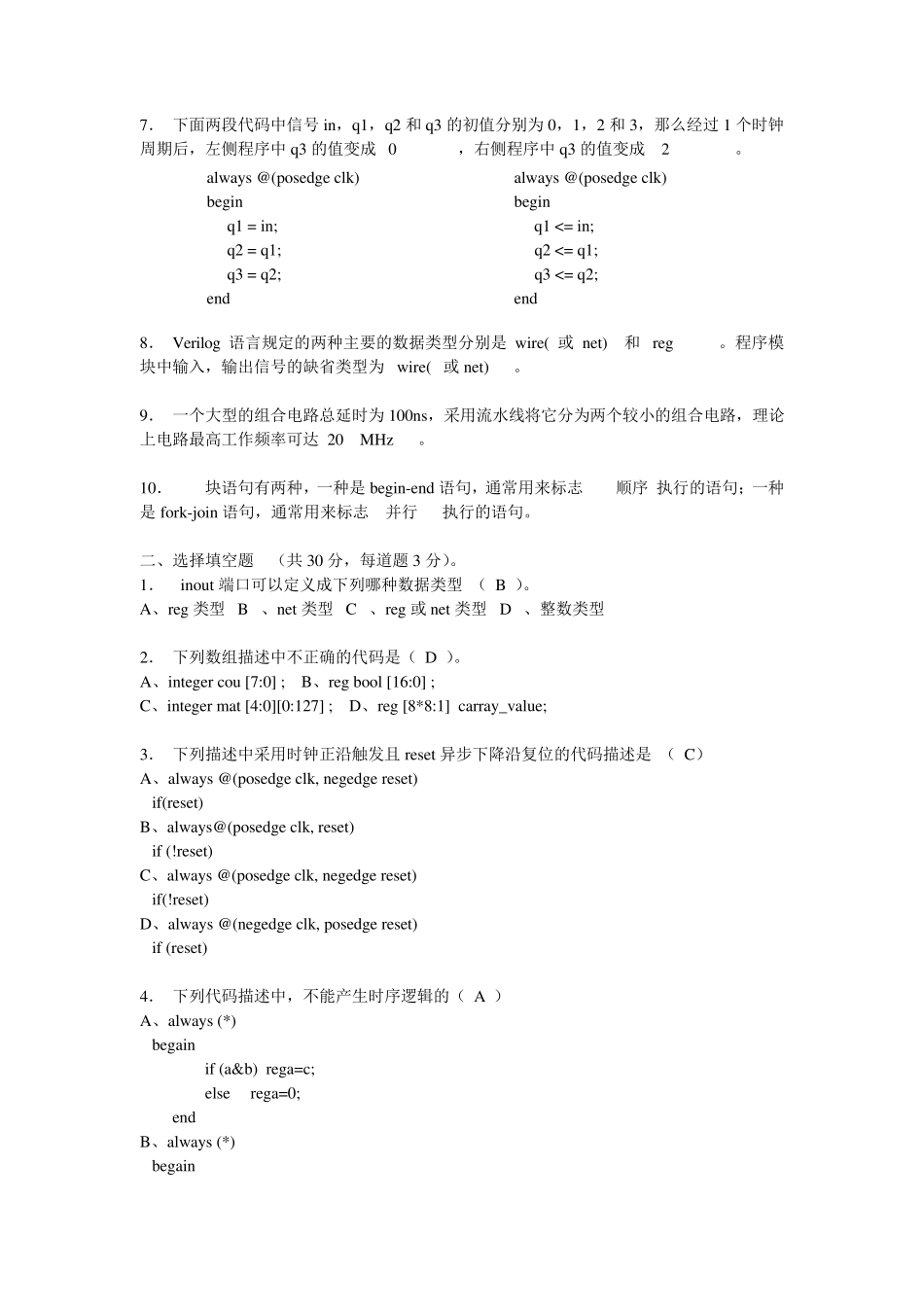

ABCDEF 2. 根据图中输入输出关系将 Verilog 模块定义补充完整,其中信号A 为 5 比特宽度,其余信号为 1 比特宽度

tblockCBA5-bit宽 3. IEEE 标准的硬件描述语言是 verilog HDL 和 VHDL

4. 你所知道的可编程逻辑器件有(至少两种): FPGA, CPLD, GAL, PAL(任写其二)

5. 假定某 4 比特位宽的变量 a 的值为 4’b1011,计算下列运算表达式的结果 6. Verilog 语言规定了逻辑电路中信号的 4 种状态,分别是 0,1,X 和 Z

其中 0 表示低电平状态,1 表示高电平状态,X 表示 不定态(或未知状态) ,Z 表示 高阻态

assign F= E ^ ( (A&B) | (

(C&D))) module tblock( A,B,C ) ; output [4:0] A; input B; inout C; … … //省略了功能描述 endmodule // 模块结束 &a = 1’b0 ~a = 4’b0100 {3{a}} = 12’b101110111011 {a[2:0],a[3]} = 4’b0111 (a=a) = 1’b1

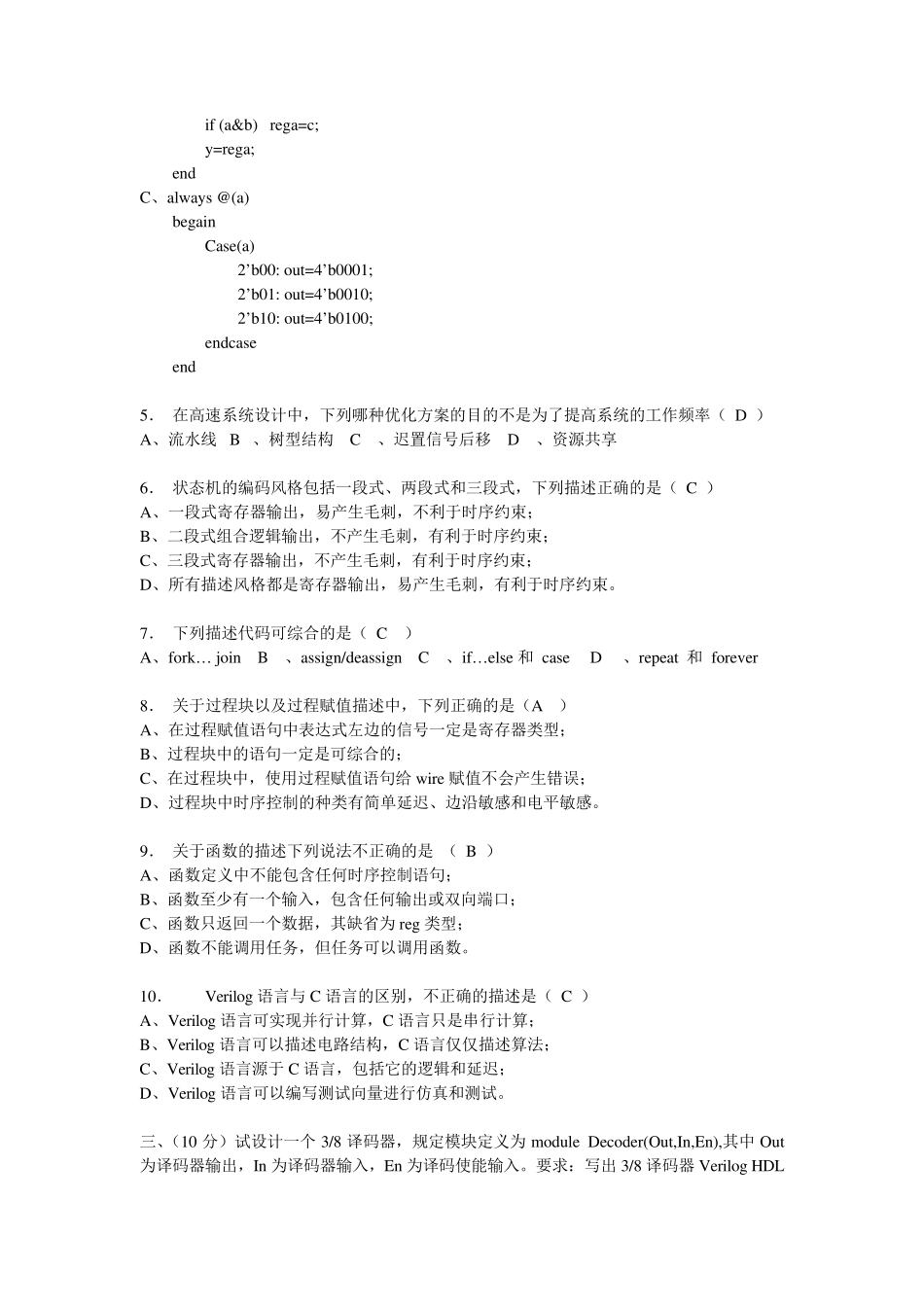

a = 1’b0 7. 下面两段代码中信号in,q1,q2 和q3 的初值分别为0,1,2 和3,那么经过1 个时