1 / 17 项目一 数 据 选 择 器 一、实验与设计要求 1.熟悉 MAX+PLUS II的编译环境,掌握该集成环境各个菜单项的使用; 2.了解 MAX+PLUSII的 VHDL程序设计输入方法,初步了解该软件的仿真环境; 3.初步运用 VHDL编程,体会硬件描述语言的先进性; 4.理解 VHDL语言的并发执行的特点; 5.熟悉 VHDL语法 6

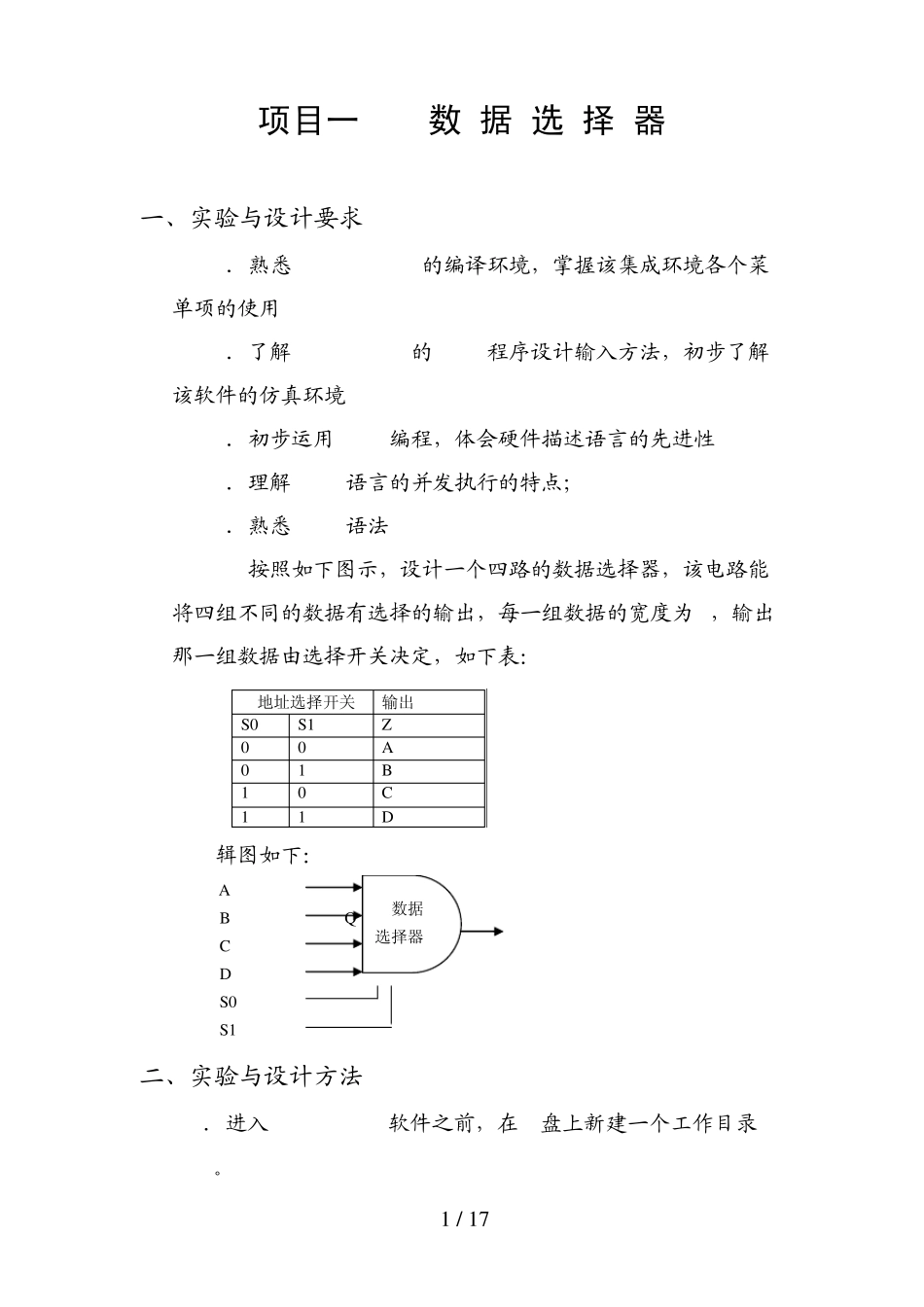

按照如下图示,设计一个四路的数据选择器,该电路能将四组不同的数据有选择的输出,每一组数据的宽度为 4,输出那一组数据由选择开关决定,如下表: 辑图如下: A B Q C D S0 S1 二、实验与设计方法 1.进入 MAX+PLUSII软件之前,在 E盘上新建一个工作目录\lyung

地址选择开关 输出 S0 S1 Z 0 0 A 0 1 B 1 0 C 1 1 D 数据 选择器 2 / 1 7 2.进入MAX+PLUSII文本编辑器,编写VHDL程序,并保存文件至\lyung\ mux41

vhd: 3

将工程指向当前文件并编译当前文件

建立波形仿真文件,设臵输入、输出端口及输入端口的信号波形,保存波形仿真文件

进入仿真器工作环境,查看波形仿真结果

选择器件, 为电路端口分配 FPGA器件引脚

进行第二次编译(包括逻辑综合和器件工艺映射),生成目标文件(*

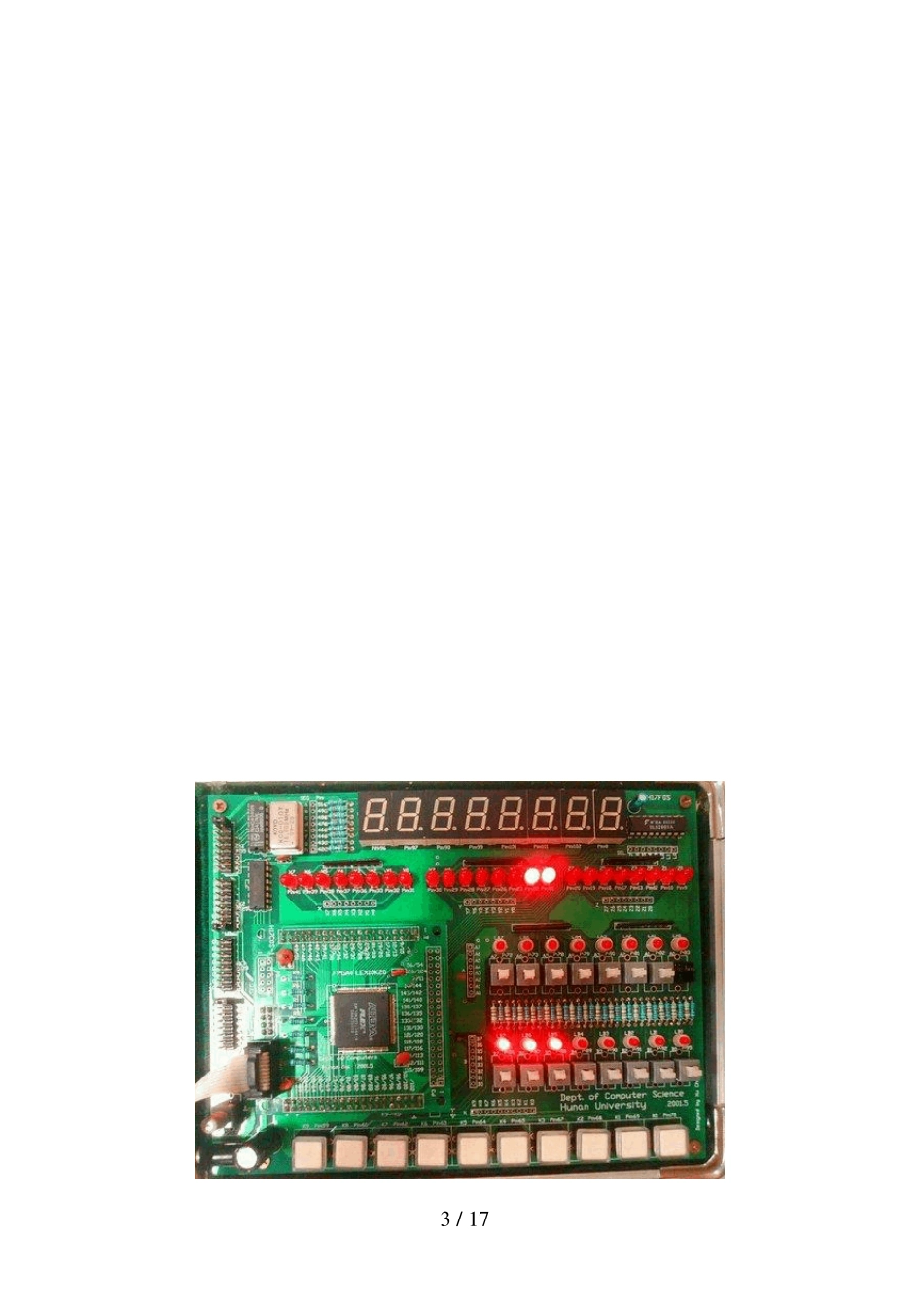

8.将目标文件下载至FPGA器件

9.在实验台上进行实际操作,验证设计的正确性

三、实验与设计结果 通过实验,初步熟悉了 MAX+PLUS II的编译环境,并掌握该集成环境各个菜单项的使用

实验过程中,了解了 MAX+PLUSII的 VHDL程序设计输入方法,初步运用 VHDL编程,成功的按照实验要求设计了程序的 VHDL源码(见附件1),熟悉了 VHDL语法,理解了 VHDL语言的并发执行的特点;并进行了仿真实验