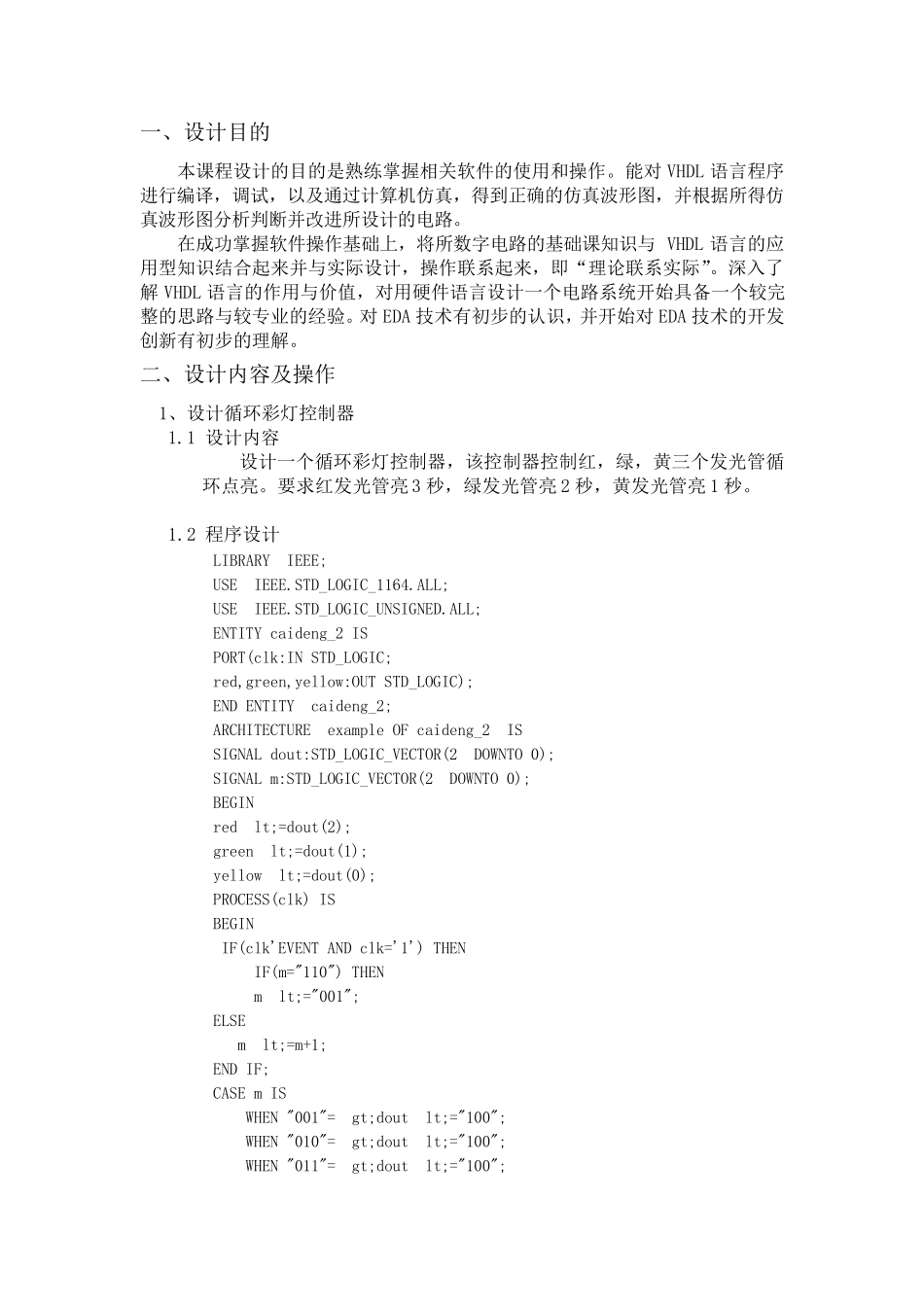

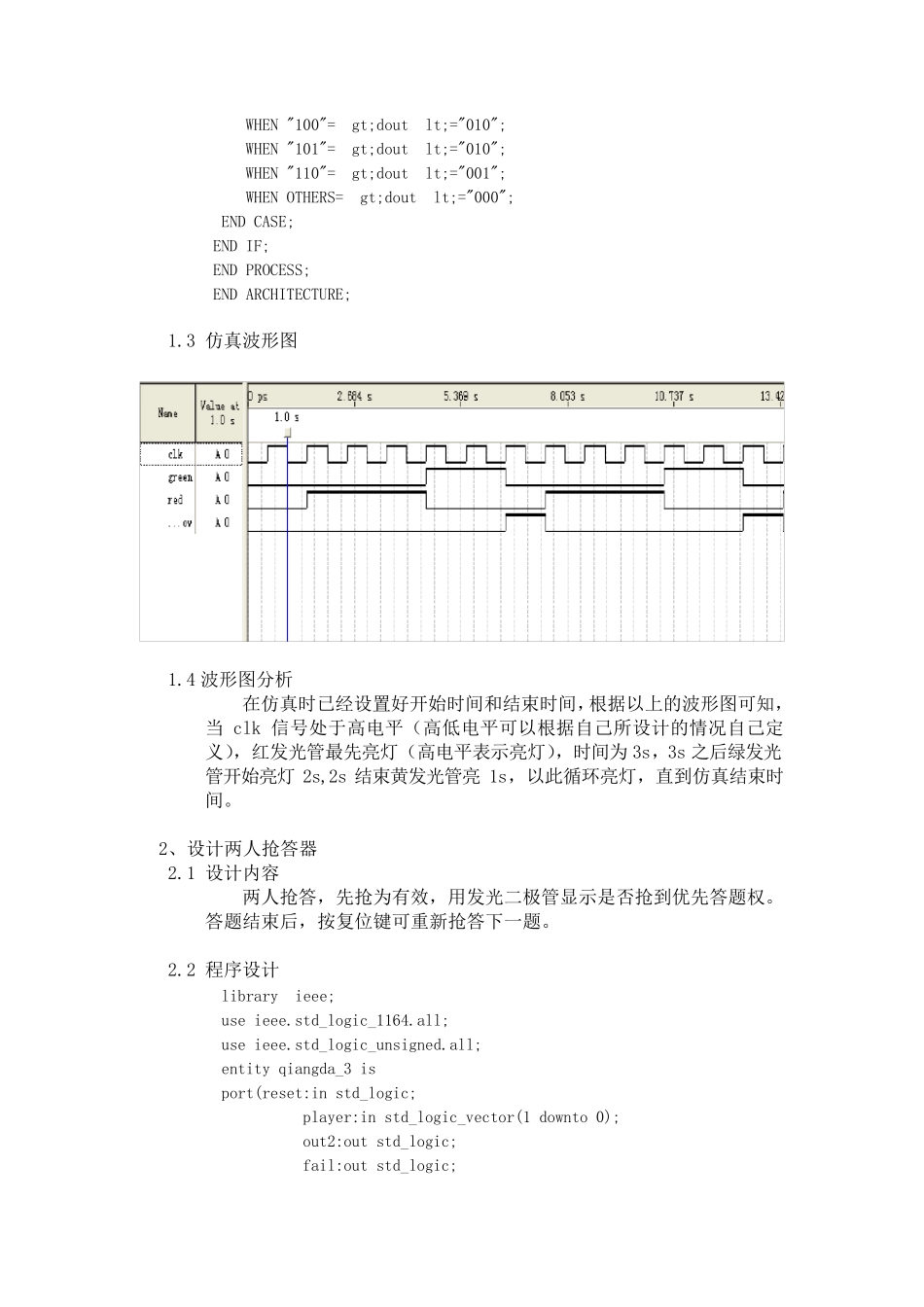

一、设计目的 本课程设计的目的是熟练掌握相关软件的使用和操作。能对VHDL 语言程序进行编译,调试,以及通过计算机仿真,得到正确的仿真波形图,并根据所得仿真波形图分析判断并改进所设计的电路。 在成功掌握软件操作基础上,将所数字电路的基础课知识与VHDL 语言的应用型知识结合起来并与实际设计,操作联系起来,即“理论联系实际”。深入了解 VHDL 语言的作用与价值,对用硬件语言设计一个电路系统开始具备一个较完整的思路与较专业的经验。对EDA 技术有初步的认识,并开始对EDA 技术的开发创新有初步的理解。 二、设计内容及操作 1、设计循环彩灯控制器 1.1 设计内容 设计一个循环彩灯控制器,该控制器控制红,绿,黄三个发光管循环点亮。要求红发光管亮 3 秒,绿发光管亮 2 秒,黄发光管亮 1 秒。 1.2 程序设计 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY caideng_2 IS PORT(clk:IN STD_LOGIC; red,green,yellow:OUT STD_LOGIC); END ENTITY caideng_2; ARCHITECTURE example OF caideng_2 IS SIGNAL dout:STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL m:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN red<=dout(2); green<=dout(1); yellow<=dout(0); PROCESS(clk) IS BEGIN IF(clk'EVENT AND clk='1') THEN IF(m="110") THEN m<="001"; ELSE m<=m+1; END IF; CASE m IS WHEN "001"=>dout<="100"; WHEN "010"=>dout<="100"; WHEN "011"=>dout<="100"; WHEN "100"=>dout<="010"; WHEN "101"=>dout<="010"; WHEN "110"=>dout<="001"; WHEN OTHERS=>dout<="000"; END CASE; END IF; END PROCESS; END ARCHITECTURE; 1.3 仿真波形图 1.4 波形图分析 在仿真时已经设置好开始时间和结束时间,根据以上的波形图可知,当clk 信号处于高电平(高低电平可以根据自己所设计的情况自己定义),红发光管最先亮灯(高电平表示亮灯),时间为3s,3s 之后绿发光管开始亮灯2s,2s 结束黄发光管亮1s,以此循环亮灯,直到仿真结束时间。 2、设计两人抢答器 2.1 设计内容 两人抢答,先抢为有效,用发光二极管显示是否抢到优先答题权。答题结束后,按复位键可重新抢答下一题。 2.2 程序设计 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity qiangda_3 is port(reset:i...