© Copyright 2015 Xilinx Page 1 XDC 约束技巧之I/O 篇 (上) 《XDC约束技巧之时钟篇》中曾对I/O 约束做过简要概括,相比较而言,XDC 中的I/O 约束虽然形式简单,但整体思路和约束方法却与UCF 大相径庭

加之FPGA 的应用特性决定了其在接口上有多种构建和实现方式,所以从 UCF 到 XDC 的转换过程中,最具挑战的可以说便是本文将要讨论的I/O 约束了

I/O 约束的语法 XDC 中可以用于 I/O 约束的命令包括set_inpu t_delay / set_ou tpu t_delay 和set_max _delay / set_min_delay

其中,只有那些从 FPGA 管脚进入和/或输出都不经过任何时序元件的纯组合逻辑路径可以用 set_max _delay / set_min_delay 来约束,其余 I/O 时序路径都必须由 set_inpu t_delay / set_ou tpu t_delay 来约束

如果对FPGA 的I/O 不加任何约束,Viv ado 会缺省认为时序要求为无穷大,不仅综合和实现时不会考虑 I/O 时序,而且在时序分析时也不会报出这些未约束的路径

本文以下章节将会着重讨论 XDC 接口约束和时序分析的基础,介绍如何使用set_inpu t_delay / set_ou tpu t_delay 对FPGA 的I/O 时序进行约束

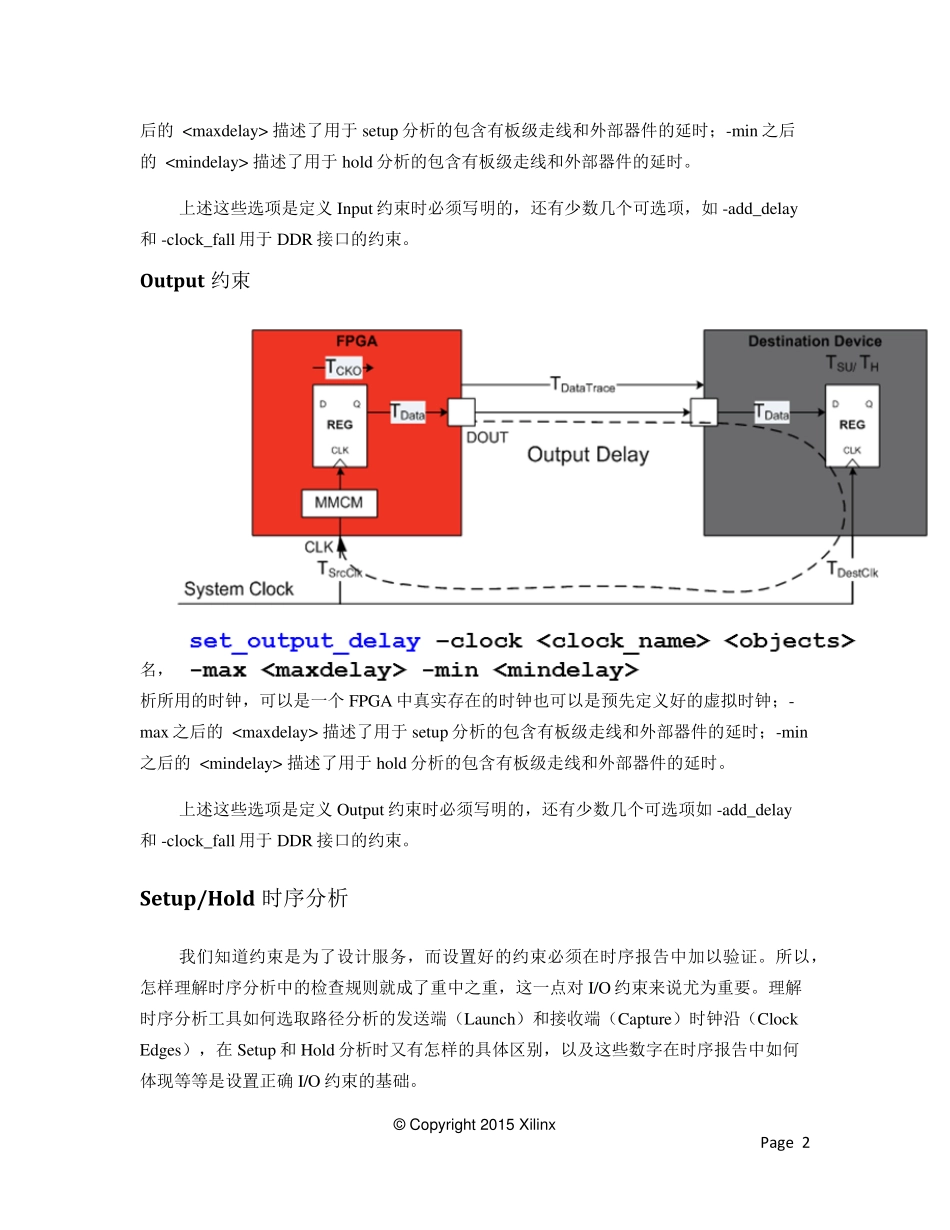

Inpu t 约束 上图所示 set_input_delay 的基本语法中, 是想要设定 inpu t 约束的端口名,可以是一个或数个 port;-clock 之后的 指明了对 时序进行分析所用的时钟,可以是一个 FPGA 中真实存在的时钟也可以是预先定义好的虚拟时钟;-max 之 © Copyright 2015 Xilinx Page 2 后的 描述了