准备好要用来生成ip 核的模块 2

在菜单栏中选择“工具”(Tools)菜单,选择子菜单中的“生成并封装 IP”(Create and Package IP)

如图 1 所示

选择相应的菜单项 3

点击菜单项后出现如图 2 中向导窗口

选择菜单项之后出现的向导窗口 4

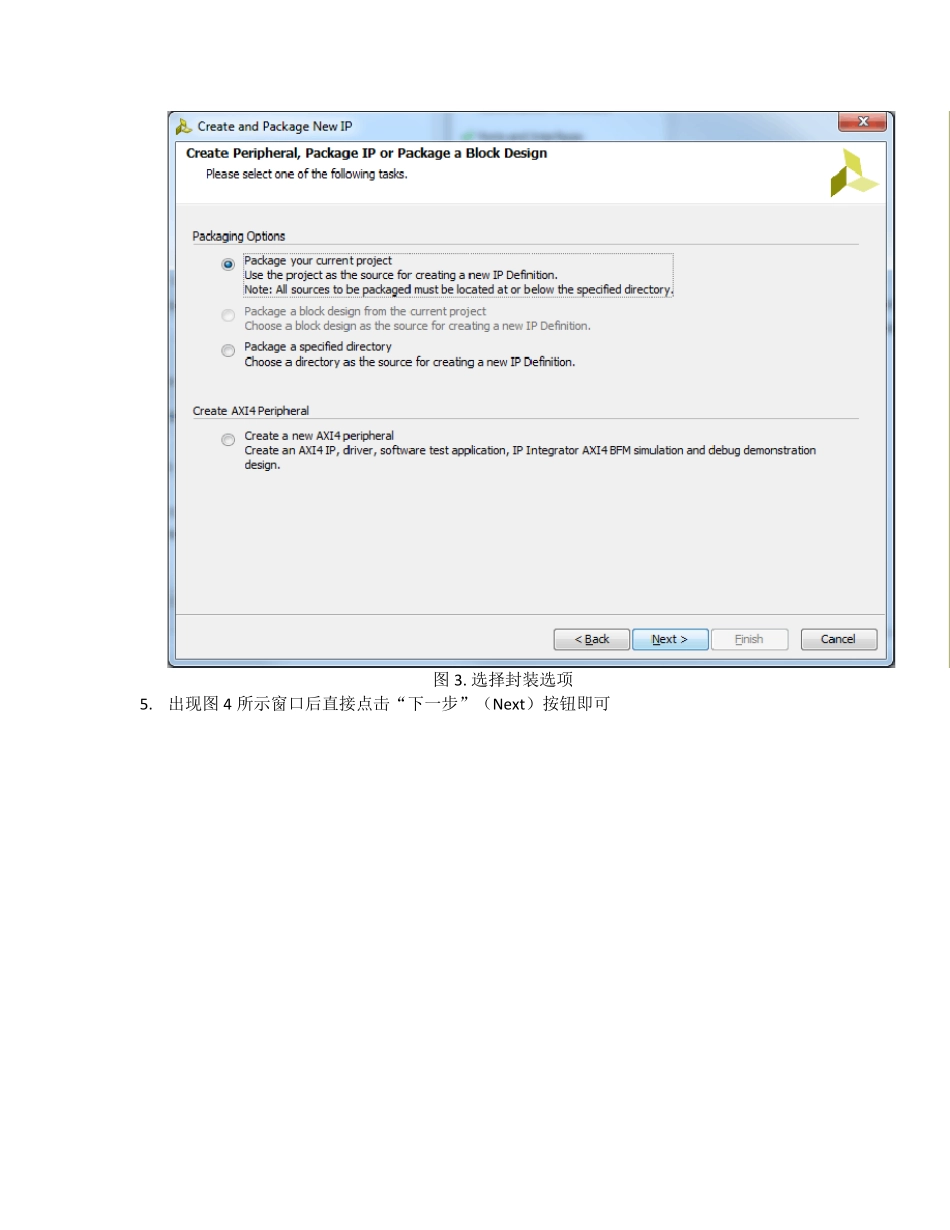

由于我是直接将一个工程打包成一个模块,然后供其他工程使用,所以在图2 中点击“下一步”(Next)按钮之后出现的窗口中我选择“打包封装当前项目”(Package your current project)选项并点击“下一步”(Next)按钮,如图3 所示

选择封装选项 5

出现图4 所示窗口后直接点击“下一步”(Next)按钮即可 图4

IP 存放路径 6

最后就是确定生成IP 了 图5

IP 生成向导确定窗口 7

之后出现封装IP 相关的一些信息,如图6 所示

在图6 中可以设置 IP 核的名称等信息

图6 中左侧依次列出了一些信息

IP 核信息页面 8

图7 为IP 核兼容性页面,我使用的是zed board,所以这里出现的是zynq 芯片 图7

IP 核兼容性信息 9

图8 为IP 核接口信息,图中显示了我所要封装的IP 核的引脚 图8

IP 核接口信息 10

图9 为封装完毕后IP 核的图形模块,在原理图调用时会显示 图9

封装原理图 11

最下面是该IP 核的一个摘要,此时IP 核还没有生成,需要在“预览和生成”(Review and Package)页面点击“封装IP”(Package IP)按钮,如图10 下部分所示

由于截图过程中IP 核已经生成,所以图10 中显示的是重新封装IP(Re-Package IP)

预览并生成IP 核 至此IP 核就完全生成了,下面就是如何调用IP 核了

首先打开工程,我