1 逻辑信号电平测试器的设计目的 1

2 课程设计的组成部分 2

逻辑信号电平测试器的设计内容 2

1 输入和逻辑判断电路设计 2

2 音响产生电路设计 2

3 扬声器驱动电路设计 2

4 元器件选择 2

5 总电路设计 3

1 所遇到的问题及解决办法 3

2 收获及体会 3

3 参考文献及资料 4

教师评语 5

概述 本文介绍一种用于数字电路逻辑信号电平测试的测试器电路设计

这种逻辑信号电平测试器用来对遥控系统中的数字信号电平的高低和脉冲信号的有无进行准确的检测

在检修数字集成电路组成的设备时,经常需要用万用表和示波器对电路中的故障部位的高地电平进行测量,以便分析故障原因

使用这些仪器能较准确地测出被测点信号电平的高地和被测信号的周期,但是使用者必须一方面用眼睛看着万用表的表盘或示波器的屏幕,另一方面还要寻找测试点,因此使用起来很不方便

本次设计的仪器采用声音来表示被测信号的逻辑状态,高电平和低电平分别用不同声调的声音表示,使用者无须分神去看万用表的表盘或示波器的荧光屏

1 逻辑信号电平测试器的设计目的 (1)学习逻辑判断电路的设计方法 (2)研究逻辑判断电路的设计方案 (3)掌握逻辑判断电路的原理和使用方法 1

2 课程设计的组成部分 1

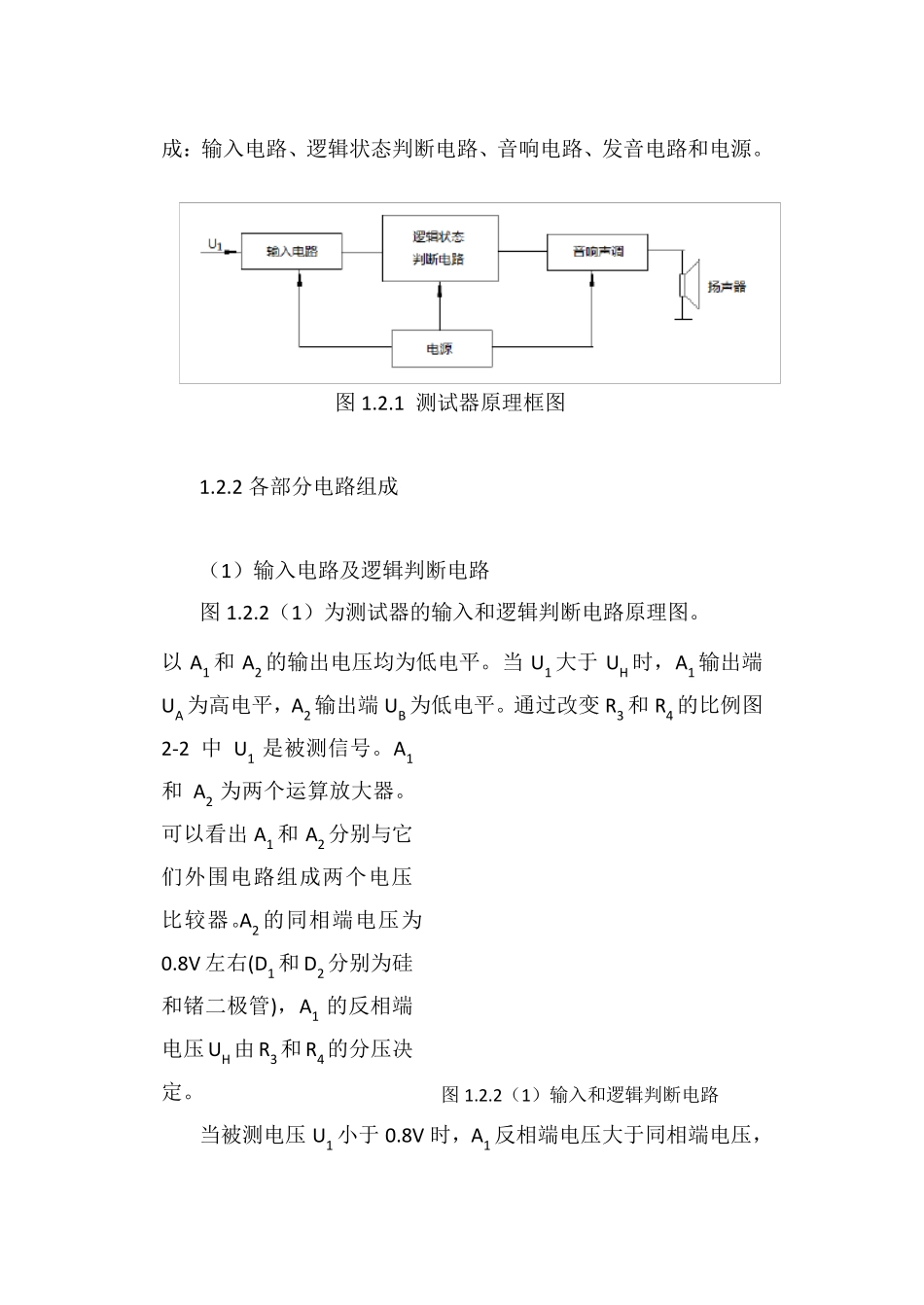

1 电路组成及工作原理 图 1

1 为测试器的原理框图

由图可以看出电路由五部分组成:输入电路、逻辑状态判断电路、音响电路、发音电路和电源

1 测试器原理框图 1

2 各部分电路组成 (1)输入电路及逻辑判断电路 图 1

2(1)为测试器的输入和逻辑判断电路原理图

以 A1 和 A2 的输出电压均为低电平

当 U1 大于 UH 时,A1 输出端UA 为高电平,A2 输出端 UB 为低电平

通过改变 R3 和 R4 的比例图2-2 中 U1 是被测信号