了解LPC2103芯片的时钟系统

分清晶振频率(FOSC)、处理器时钟(Fcclk)、系统外设时钟(Fpclk)、CCO 时钟

通过对锁相环PLL 和VPB分频器的配置,实现我们想要的时钟系统

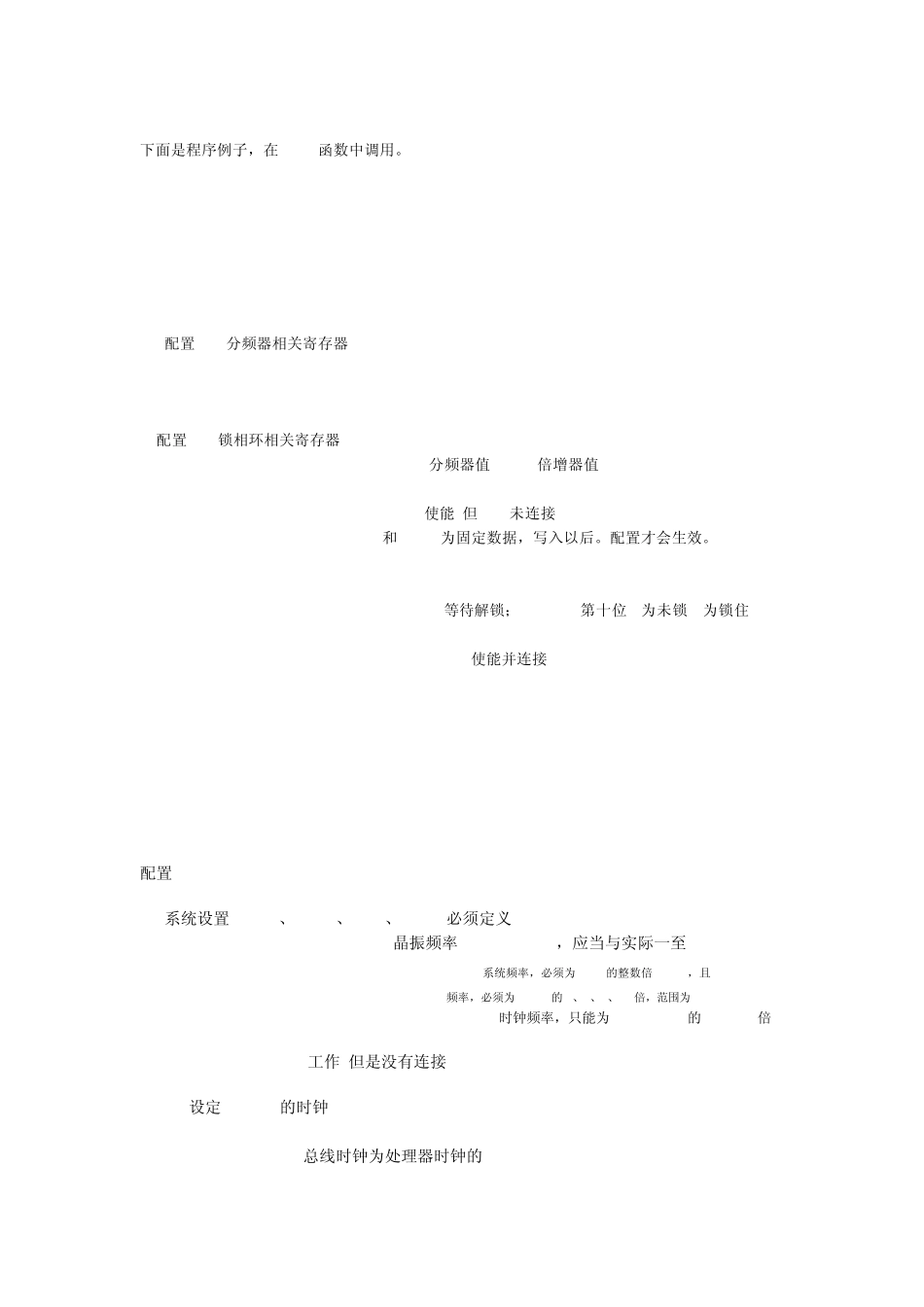

先看下面的图

(图一 几种频率的关系

括号里是有关的寄存器名) PLL 锁相环:可以通过PLL 升频和增强抗干扰性能

VPB分频器: 对PLL 时钟分频,供给片上外设使用

区分下面四种时钟频率的概念: 晶振频率(FOSC):外部晶振的频率,我们的板子焊的是11

0592M的

处理器时钟(Fcclk):芯片执行指令的频率

Fcclk = FOSC × PLL 倍频

相关寄存器:PLLCFG[4:0]

VPB时钟(Fpclk):给片内外设提供的时钟频率

Fpclk=Fcclk/PLL分频

相关寄存器:APBDIV CCO 时钟:不用管它是干什么的

只要把它设置成 156MHz~320MHz就行

相关寄存器:PLLCFG[6:5] PLL 配置需要的寄存器如下: PLLCON:PLL 控制寄存器

控制 PLL 使能和PLL 连接的状态

PLLCFG:PLL 配置寄存器

设置PLL 倍频和PLL 分频

PLLSTAT:PLL 状态寄存器

只读寄存器,读出 PLL 状态

PLLFEED:PLL 馈送寄存器

将值 0xAA、0x55写入 PLLFEED,才能使PLLCON和 PLLCFG的配置生效

VPB配置需要的寄存器 APBDIV:VPB分频器

计算频率值: Fosc = 11

0592MHz //外部晶振频率 Fcclk = 11

0592*6 = 66

3552MHz //处理器时钟(Fcclk)必须低于芯片的最高频率70MHz Fpclk = Fcclk/4 = 16

5888MHz //VPB时钟(Fpclk) Fcco = 66

3552*2*P