SpartanIIE 内部锁相环(DLL)的使用 以下是一个实验,讲述如何使用器件内部锁相环(DLL),很有实际意义,所以拿出来,大家一起学习,一起进步

实验 SpartanIIE 内部锁相环(DLL)的使用 一、实验目的 1. 进一步熟悉 FPGA 软硬件开发环境; 2. 了解 FPGA 的内部结构; 3. 初步掌握 DLL 的使用

二、设计任务 FPGA 中的 DLL 是一种很好的资源,特别是较高频率的时候,应用较广

它可以对时钟进行倍频、锁相等操作

通过设计掌握 DLL 的各种应用:倍频,分频,锁相,以及移相的操作,编程演示,通过示波器观察和比较波形

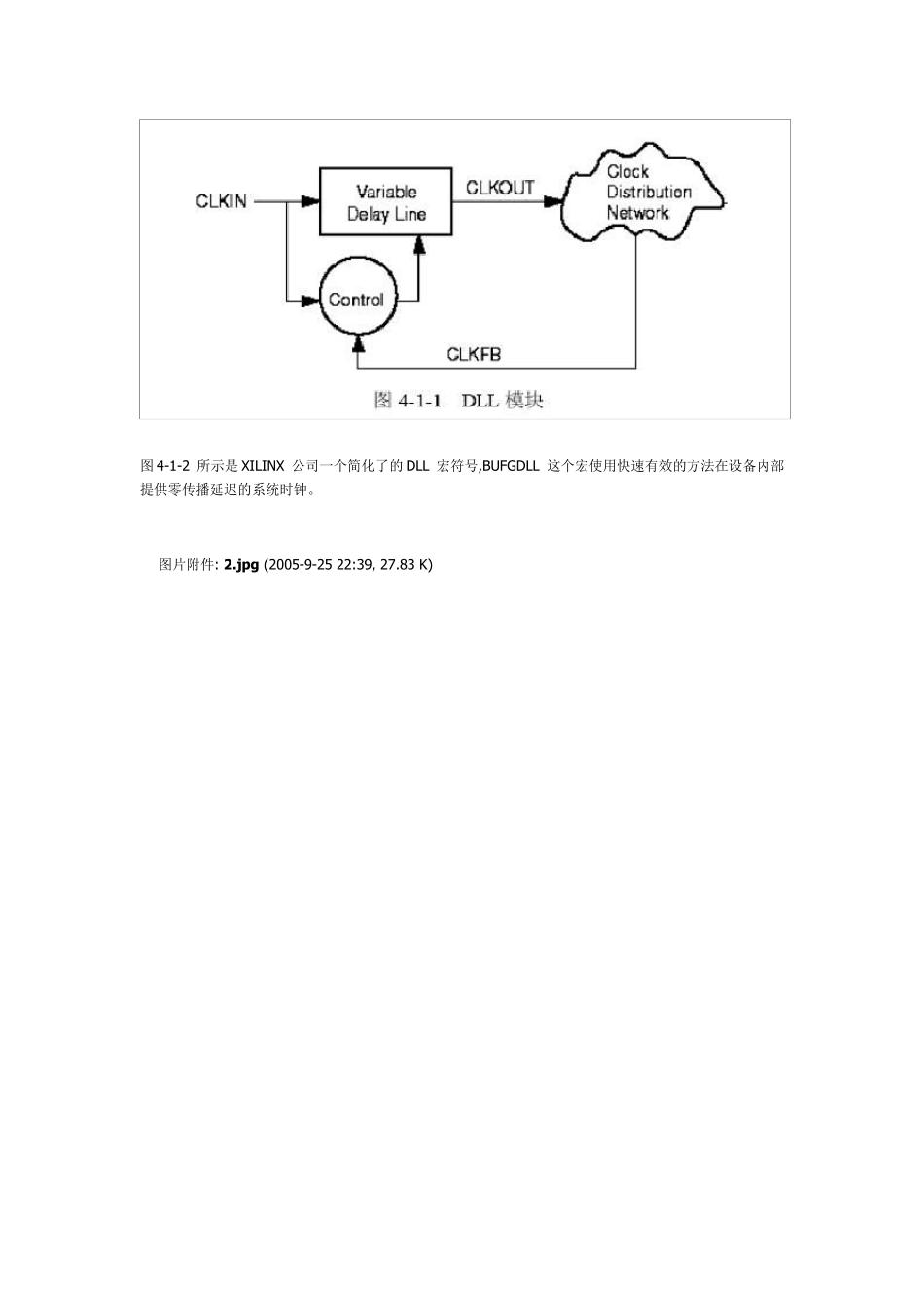

下面先对 DLL 做一个简单的介绍

1. 概述 XILINX 公司的 Spartan-IIE 系列提供四个延迟锁相环(Delay-Locked Loop),分别位于芯片内部的四个脚

这些DLL 可以被用来实现一些电路以完善和简化系统级设计,比如提供零传播延迟,低时钟相位差和高级时钟区域控制等

随着FPGA 尺寸的增加,芯片上时钟的分布质量就变得越来越重要

时钟相位差和时钟延迟严重影响设备的性能,在大的设备中用传统的时钟网络控制时钟相位差和时钟延迟变得十分困难,XILINX 公司的 Spartan-IIE 系列的四个延迟锁定环(Delay-Locked Loop)恰好解决了这个问题

每一个DLL 可以驱动两个全局时钟,全局时钟分布网络可以根据不同的负载,将时钟相位差最小化

通过观察一个 DLL 输出时钟,它可以在网络中补偿延迟,有效的消除了设备内从外部输入端口到时钟装载的延迟

除了根据用户的原时钟信号提供零延迟,DLL 还可以提供原时钟信号的若干倍频段

DLL 可以使时钟加倍,二倍频或四倍频

还可以对时钟信号进行分频,1

5,3,4,5,8,16 分频

DLL 还可以提供固定相位差的时钟,如 90°、1