下载后可任意编辑常见电平标准的讨论( TTL, ECL, PECL, LVDS、 CMOS、 CML, GTL, HSTL, SSTL) 部分资料上说它们的逻辑标准,门限都是一样的,就是供电大小不同,这两种电平的区别就是这些么

是否 LVTTL 电平无法直接驱动 TTL 电路呢

另外,"因为 2

4V 与 5V 之间还有很大空闲, 对改进噪声容限并没什么好处, 又会白白增大系统功耗, 还会影响速度

" 中,关于改进噪声容限和系统功耗部分大家还有更深化的解释么

简单列个表把 Voh Vol Vih Vil VccTTL 2

8 5CMOS 4

5 5LVTTL 2

3LVCMOS 2

3SSTL_2 1

5根据上表所示, LVTTL 能够驱动 TTL, 至于噪声, 功耗问题小弟就不理解了, 希望高手赐教

TTL 和 LVTTL 的转换电平是相同的, TTL 产生于 1970 年代初, 当时逻辑电路的电源电压标准只有 5V 一种, TTL 的高电平干扰容限比低电平干扰容限大

CMOS 在晚十几年后才形成规模生产, 转换电平是电源电压的一半

1990 年代才产生了 3

5V 等不同的电源标准, 于是重新设计了一部分 TTL 电路成为 LVTTL

LVTTLTTL 和 LVTTL 的转换电平是相同的, TTL 产生于 1970 年代初, 当时逻辑电路的电源电压标准只有 5V 一种, TTL 的高电平干扰容限比低电平干扰容限大

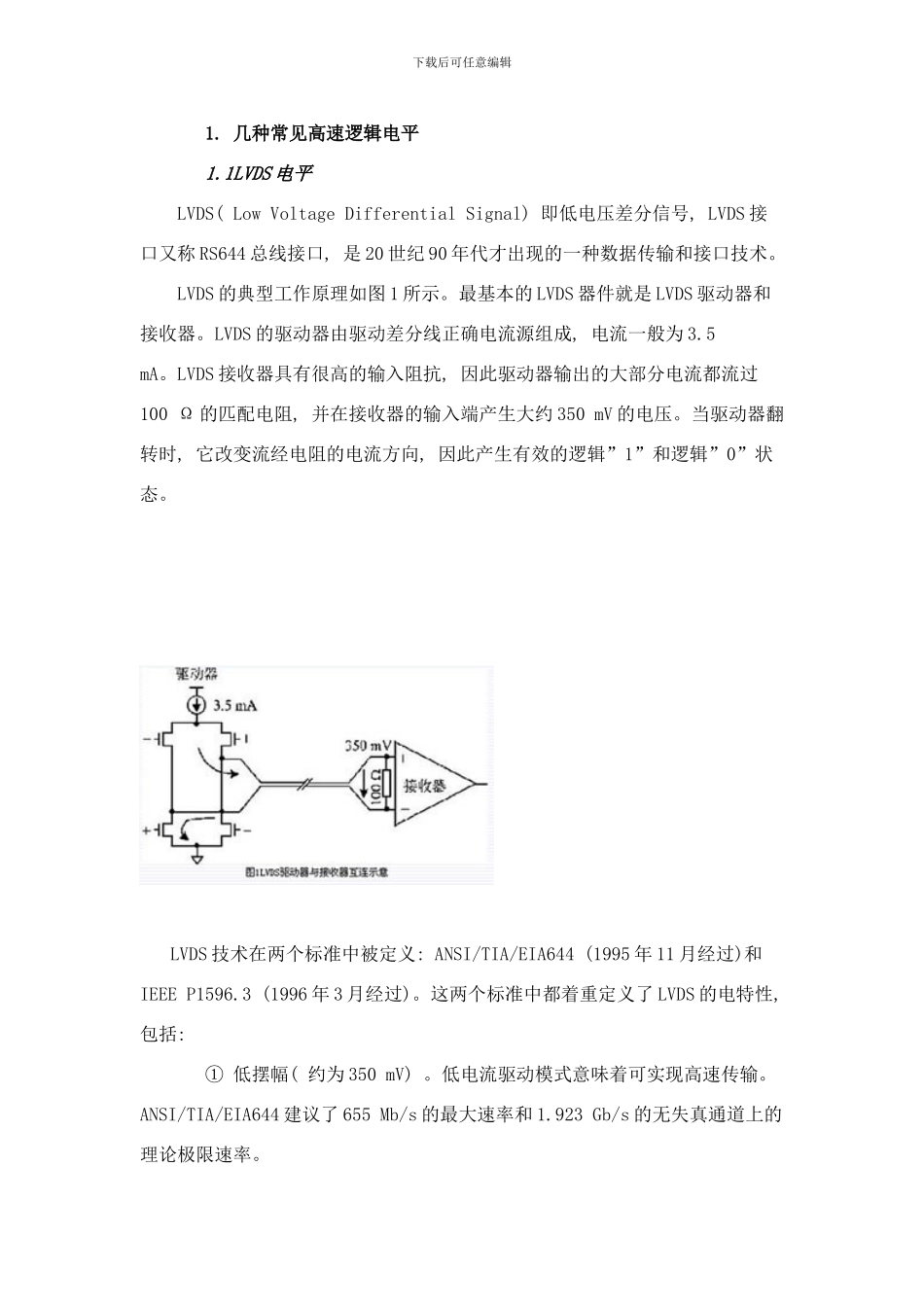

下载后可任意编辑CMOS 在晚十几年后才形成规模生产, 转换电平是电源电压的一半

1990 年代才产生了 3

5V 等不同的电源标准, 于是重新设计了一部分 TTL 电路成为