数字电子钟逻辑电路设计 一、 简述 数字电子钟是一种用数字显示秒、分、时、日的计时装置,与传统的机械钟相比,它具有走时准确,显示直观、无机械传动装置等优点,因而得到了广泛的应用

小到人们日常生活中的电子手表,大到车站、码头、机场等公共场所的大型数显电子钟

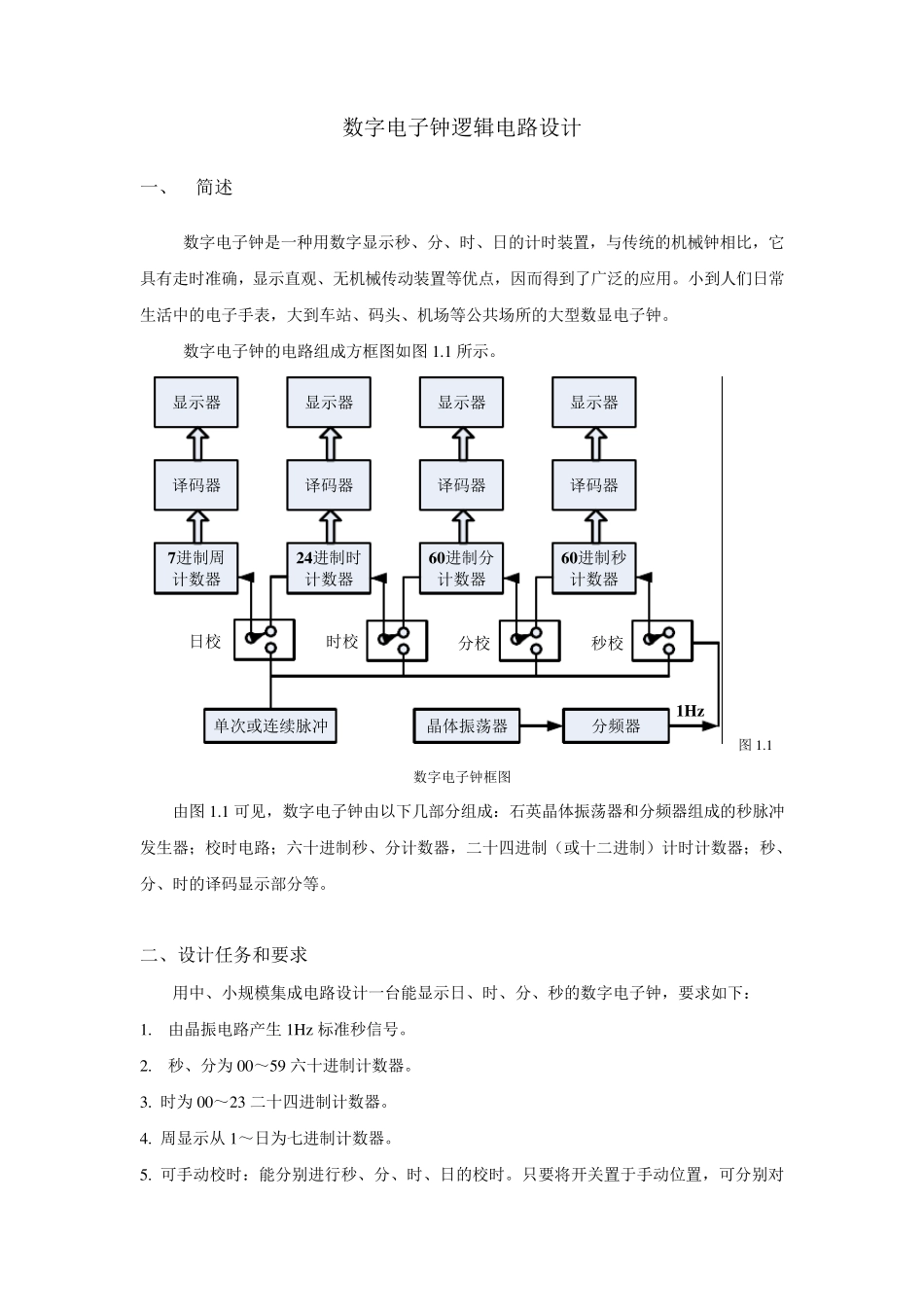

数字电子钟的电路组成方框图如图 1

显示器译码器7进制周计数器显示器译码器24进制时计数器显示器译码器60进制分计数器显示器译码器60进制秒计数器日校分校时校秒校单次或连续脉冲晶体振荡器分频器1Hz图 1

1 数字电子钟框图 由图 1

1 可见,数字电子钟由以下几部分组成:石英晶体振荡器和分频器组成的秒脉冲发生器;校时电路;六十进制秒、分计数器,二十四进制(或十二进制)计时计数器;秒、分、时的译码显示部分等

二、设计任务和要求 用中、小规模集成电路设计一台能显示日、时、分、秒的数字电子钟,要求如下: 1

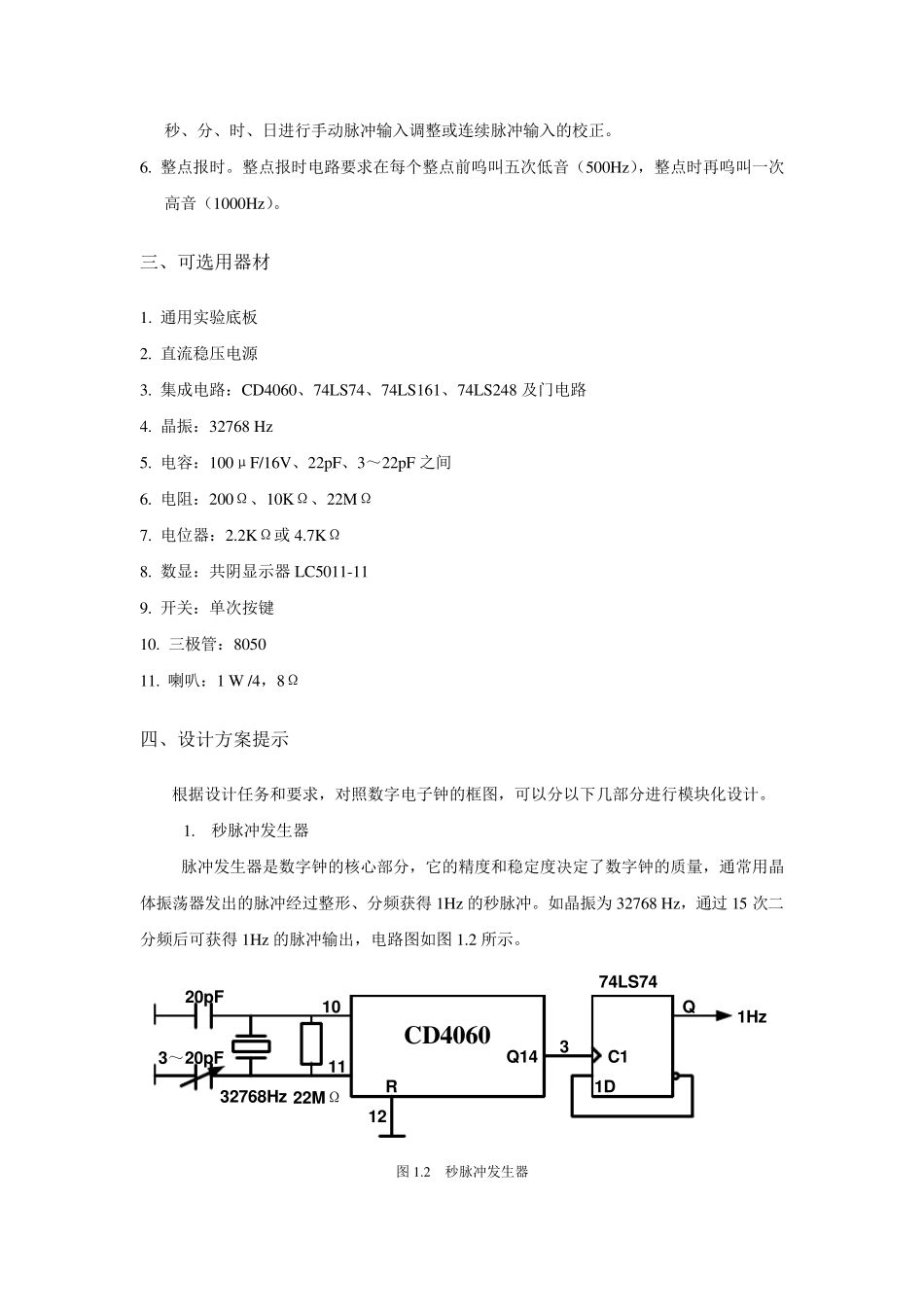

由晶振电路产生 1Hz标准秒信号

秒、分为 00~59 六十进制计数器

时为 00~23 二十四进制计数器

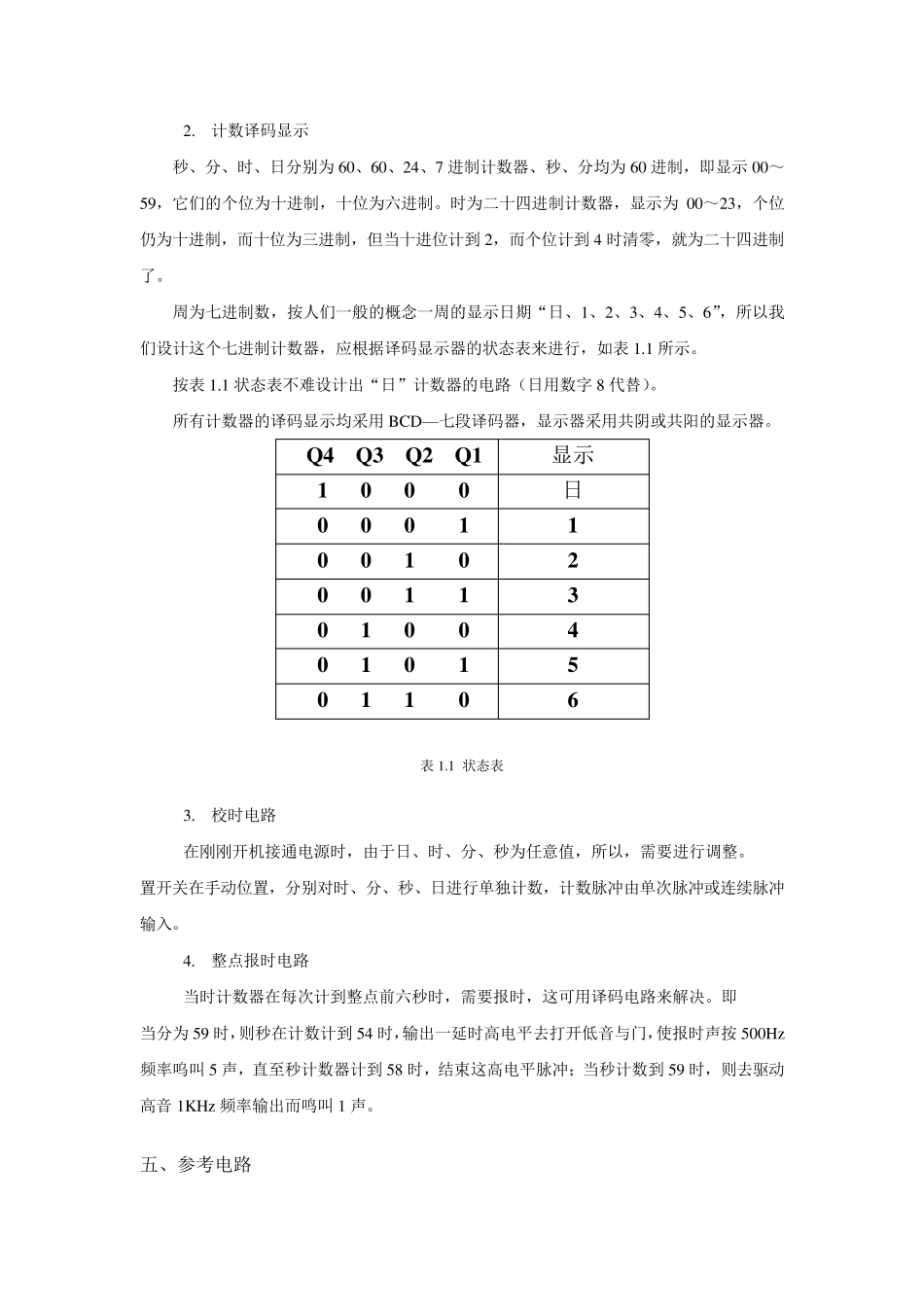

周显示从 1~日为七进制计数器

可手动校时:能分别进行秒、分、时、日的校时

只要将开关置于手动位置,可分别对秒、分、时、日进行手动脉冲输入调整或连续脉冲输入的校正

整点报时电路要求在每个整点前呜叫五次低音(500Hz),整点时再呜叫一次高音(1000Hz)

三、可选用器材 1

通用实验底板 2

直流稳压电源 3

集成电路:CD4060、74LS74、74LS161、74LS248 及门电路 4

晶振:32768 Hz 5

电容:100μF/16V、22pF、3~22pF 之间 6

电阻:200Ω、10KΩ、22MΩ 7

数显:共阴显示器LC5011-11 9

开关:单次按键 10

三极管:80