实验二 组合逻辑电路(一) 一、实验目的 加深理解用 SSI(小规模数字集成电路)构成的组合逻辑电路的分析与设计方法

二、预习要求 1.按设计步骤,根据所给器件设计实验内容 1、2 的逻辑电路图

2,弄懂图 5

3 的工作原理与设计思想

3.在附录 C 中查出 74LS00 和 74LS10 的外引线排列图

三、实验说明 组合逻辑电路是最常见的逻辑电路之一,其特点是在任一时刻的输出信号仅取决于该时刻的输入信号,而与信号作用前电路原来所处的状态无关

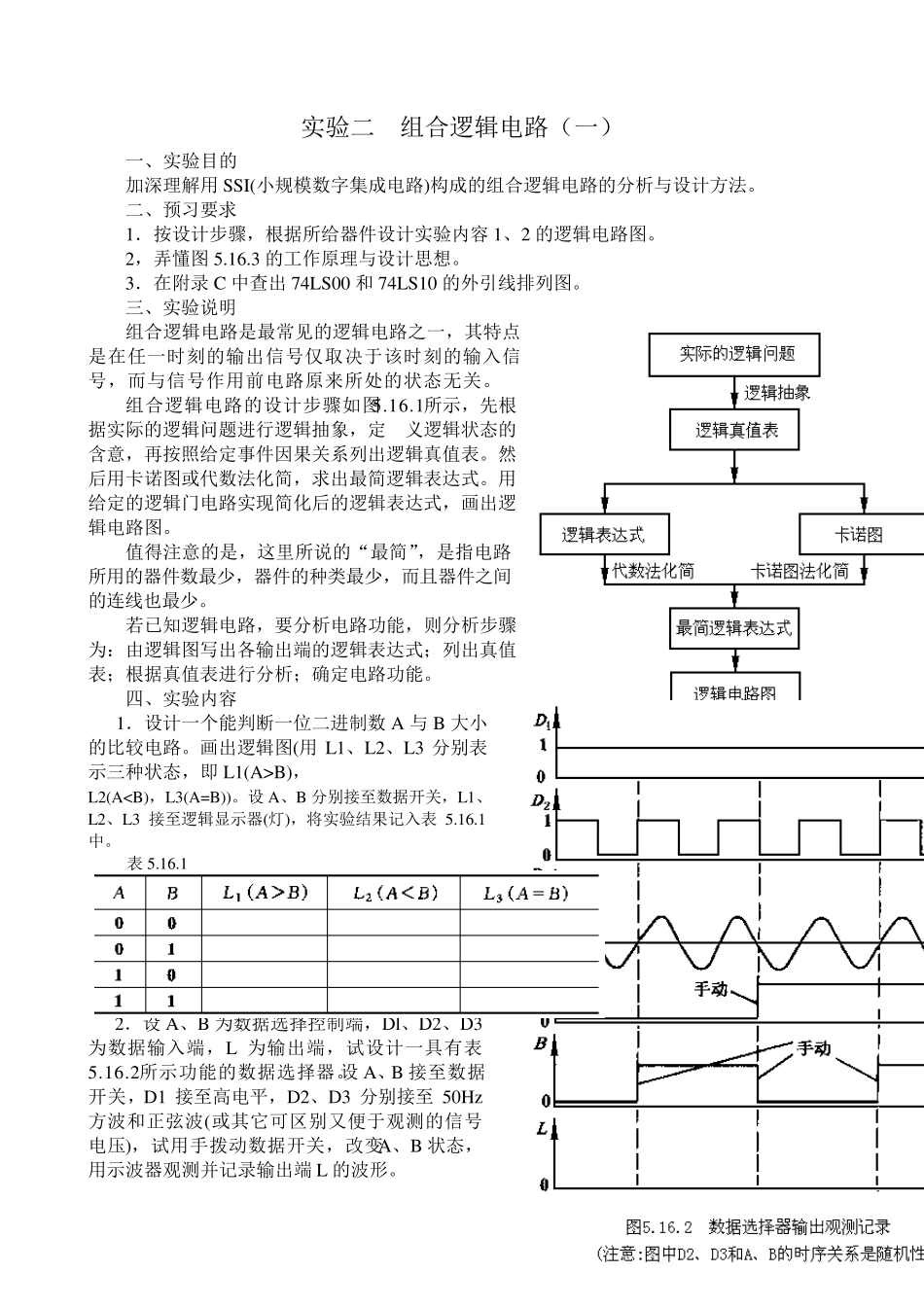

组合逻辑电路的设计步骤如图5

1所示,先根据实际的逻辑问题进行逻辑抽象,定 义逻辑状态的含意,再按照给定事件因果关系列出逻辑真值表

然后用卡诺图或代数法化简,求出最简逻辑表达式

用给定的逻辑门电路实现简化后的逻辑表达式,画出逻辑电路图

值得注意的是,这里所说的“最简”,是指电路所用的器件数最少,器件的种类最少,而且器件之间的连线也最少

若已知逻辑电路,要分析电路功能,则分析步骤为:由逻辑图写出各输出端的逻辑表达式;列出真值表;根据真值表进行分析;确定电路功能

四、实验内容 1.设计一个能判断一位二进制数 A 与 B 大小的比较电路

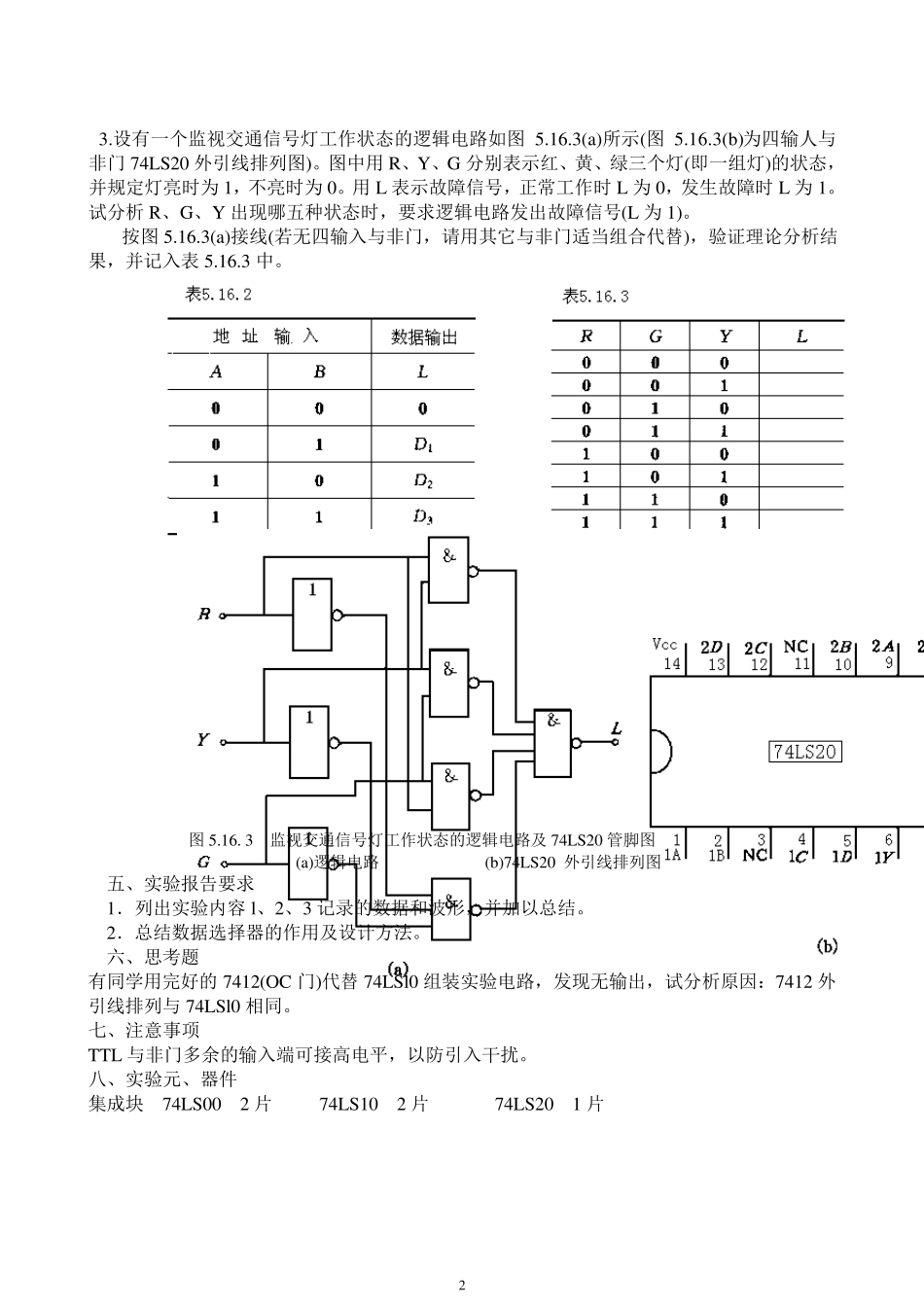

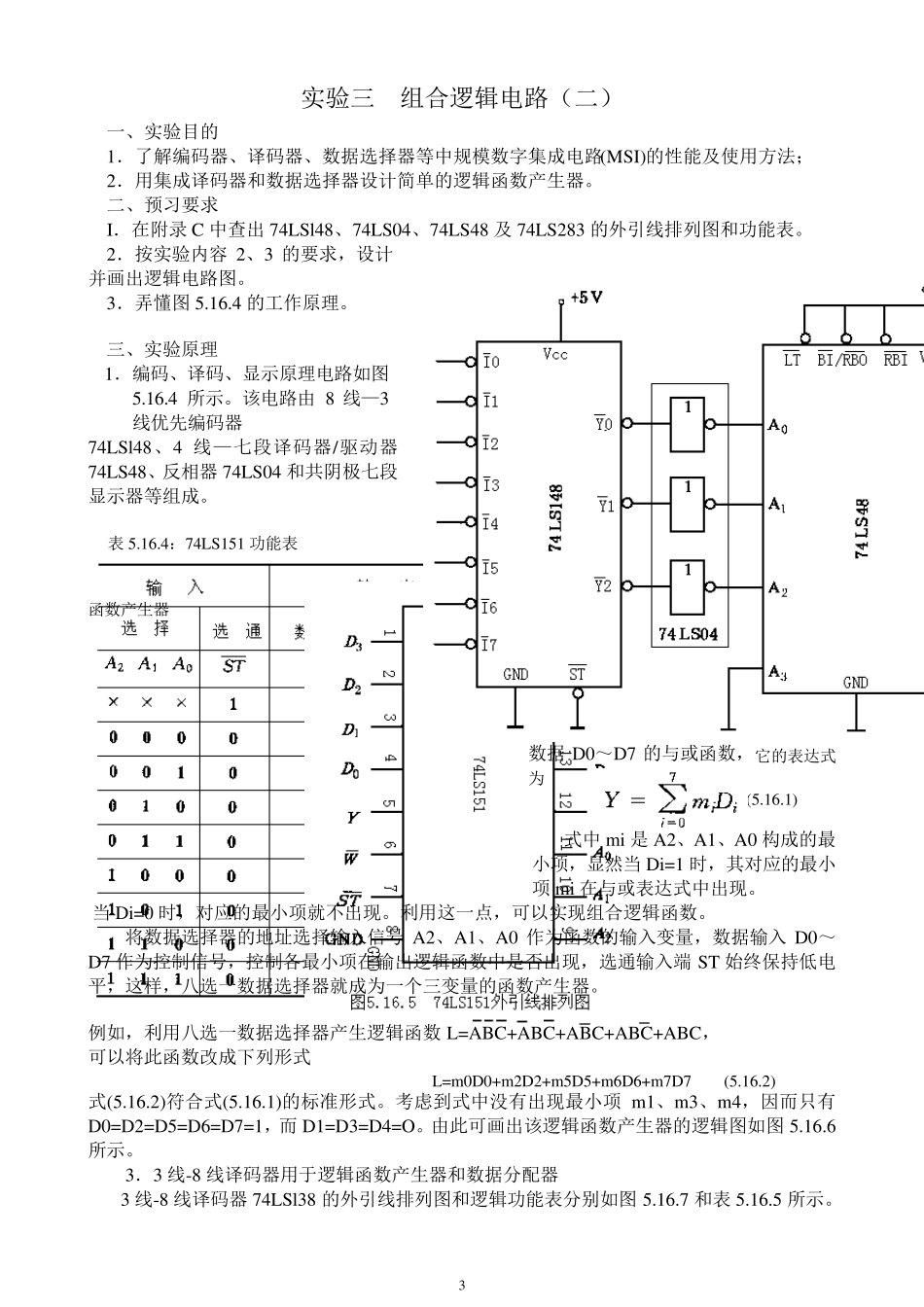

画出逻辑图(用 L1、L2、L3 分别表示三种状态,即 L1(A>B), L2(A