第三章、器件 一、超深亚微米工艺条件下 MOS 管主要二阶效应: 1、速度饱和效应:主要出现在短沟道 NMOS 管,PMOS 速度饱和效应不显著

主要原因是THGSVV太大

在沟道电场强度不高时载流子速度正比于电场强度( ),即载流子迁移率是常数

但在电场强度很高时载流子的速度将由于散射效应而趋于饱和,不再随电场强度的增加而线性增加

此时近似表达式为: (c ),csat(c ),出现饱和速度时的漏源电压DSATV是一个常数

线性区的电流公式不变,但一旦达到DSATV,电流即可饱和,此时DSI与GSV成线性关系(不再是低压时的平方关系)

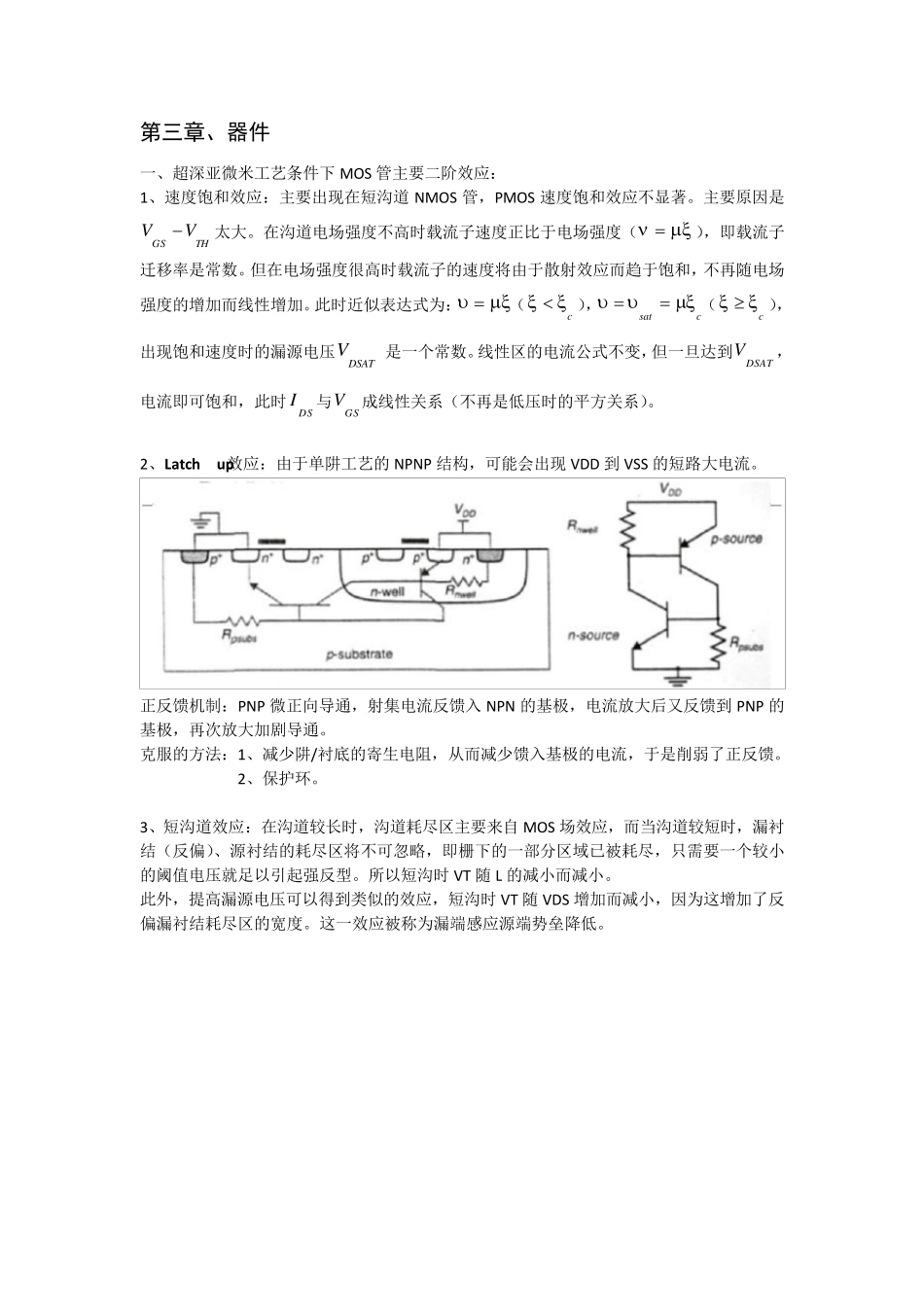

2、Latch-u p效应:由于单阱工艺的 NPNP 结构,可能会出现 VDD 到 VSS 的短路大电流

正反馈机制:PNP 微正向导通,射集电流反馈入 NPN 的基极,电流放大后又反馈到 PNP 的基极,再次放大加剧导通

克服的方法:1、减少阱/衬底的寄生电阻,从而减少馈入基极的电流,于是削弱了正反馈

3、短沟道效应:在沟道较长时,沟道耗尽区主要来自 MOS 场效应,而当沟道较短时,漏衬结(反偏)、源衬结的耗尽区将不可忽略,即栅下的一部分区域已被耗尽,只需要一个较小的阈值电压就足以引起强反型

所以短沟时 VT 随 L 的减小而减小

此外,提高漏源电压可以得到类似的效应,短沟时 VT 随 VDS 增加而减小,因为这增加了反偏漏衬结耗尽区的宽度

这一效应被称为漏端感应源端势垒降低

4、漏端感应源端势垒降低(DIBL): VDS 增加会使源端势垒下降,沟道长度缩短会使源端势垒下降

VDS 很大时反偏漏衬结击穿,漏源穿通,将不受栅压控制

5、亚阈值效应(弱反型导通):当电压低于阈值电压时 MOS 管已部分导通

不存在导电沟道时源(n+)体(p)漏(n+)三端实际上形成了一个寄生