时序逻辑电路介绍 220.什么是时序逻辑电路

答:在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路

时序逻辑电路结构示意图如图2-41所示

时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的

221.时序逻辑电路分为哪两大类

答:时序逻辑电路可分为同步时序电路和异步时序电路两大类

在同步时序逻辑电路中,存储电路内所有触发器的时钟输入端都接于同一个时钟脉冲源,因而,所有触发器的状态(即时序逻辑电路的状态)的变化都与所加的时钟脉冲信号同步

在异步时序逻辑电路中,没有统一的时钟脉冲,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化才与时钟脉冲同步,而其他触发器状态的变化并不与时钟脉冲同步

222.基本 RS触发器的组成及工作原理是怎样的

答:两个与非门电路或两个或非门电路可以组成基本 RS触发器,与非门基本 RS触发器如图 2-42所示

它以 1或 0的形式储存数据

RS触发器有两个输入端,分别称为 R端和S端,和两个互补输出端,Q和Q

当在与非门 RS触发器的输入馈入负脉冲时它就改变状态

通常两个输入相异或都是1,不能同时为 0

在s端加上零脉冲会导致输出端 Q变为高电平,同时Q会变为低电平,触发器置位,在输出存储一个 1

在R端上加上零脉冲,会导致输出端 Q变为低电平且变成高电平,这时触发器复位,在输出存储一个 0

223.什么是带时钟信号的RS触发器

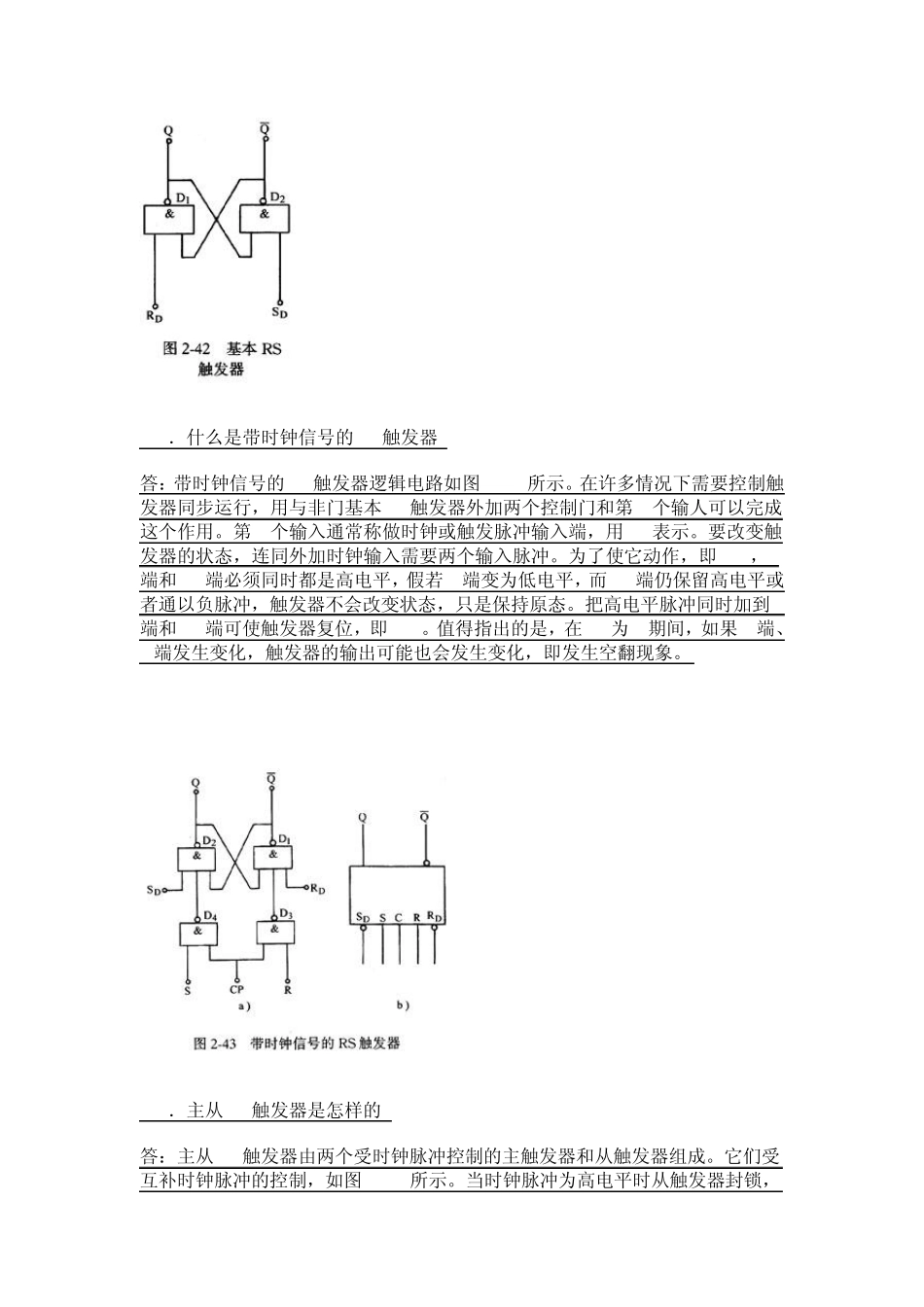

答:带时钟信号的RS触发器逻辑电路如图2-43所示

在许多情况下需要控制触发器同步运行,用与非门基本RS触发器外加两个控制门和第3个输人可以完成这个作用

第3个输入通常称做时钟或触发脉冲输入端,用CP表示

要改变触发器的状态,连同外加时钟输入需要两个输入脉冲

为了使它动作,即Q=1,S端和CP端必须同时都是高电平,假若S端