实验四触发器及其应用一、实验目的1、掌握基本RS、JK、 D 和 T 触发器的逻辑功能2、掌握集成触发器的逻辑功能及使用方法3、熟悉触发器之间相互转换的方法二、实验原理触发器具有两个稳定状态,用以表示逻辑状态“1”和“ 0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元

基本 RS 触发器图 4-1 为由两个与非门交叉耦合构成的基本RS 触发器,它是无时钟控制低电平直接触发的触发器

基本 RS 触发器具有置“0”、置“ 1”和“保持”三种功能

通常称S为置“ 1”端,因为S=0( R=1)时触发器被置“1”; R为置“ 0”端,因为 R=0( S=1)时触发器被置“0”,当 S= R= 1 时状态保持;S= R=0 时,触发器状态不定,应避免此种情况发生

基本 RS 触发器

也可以用两个“或非门”组成,此时为高电平触发有效

表 4- 1 输入输出Qn+1Qn+10 1 1 0 1 0 0 1 1 1 QnQn0 0 φφ触发器在输入信号为双端的情况下,JK 触发器是功能完善、使用灵活和通用性较强的一种触发器

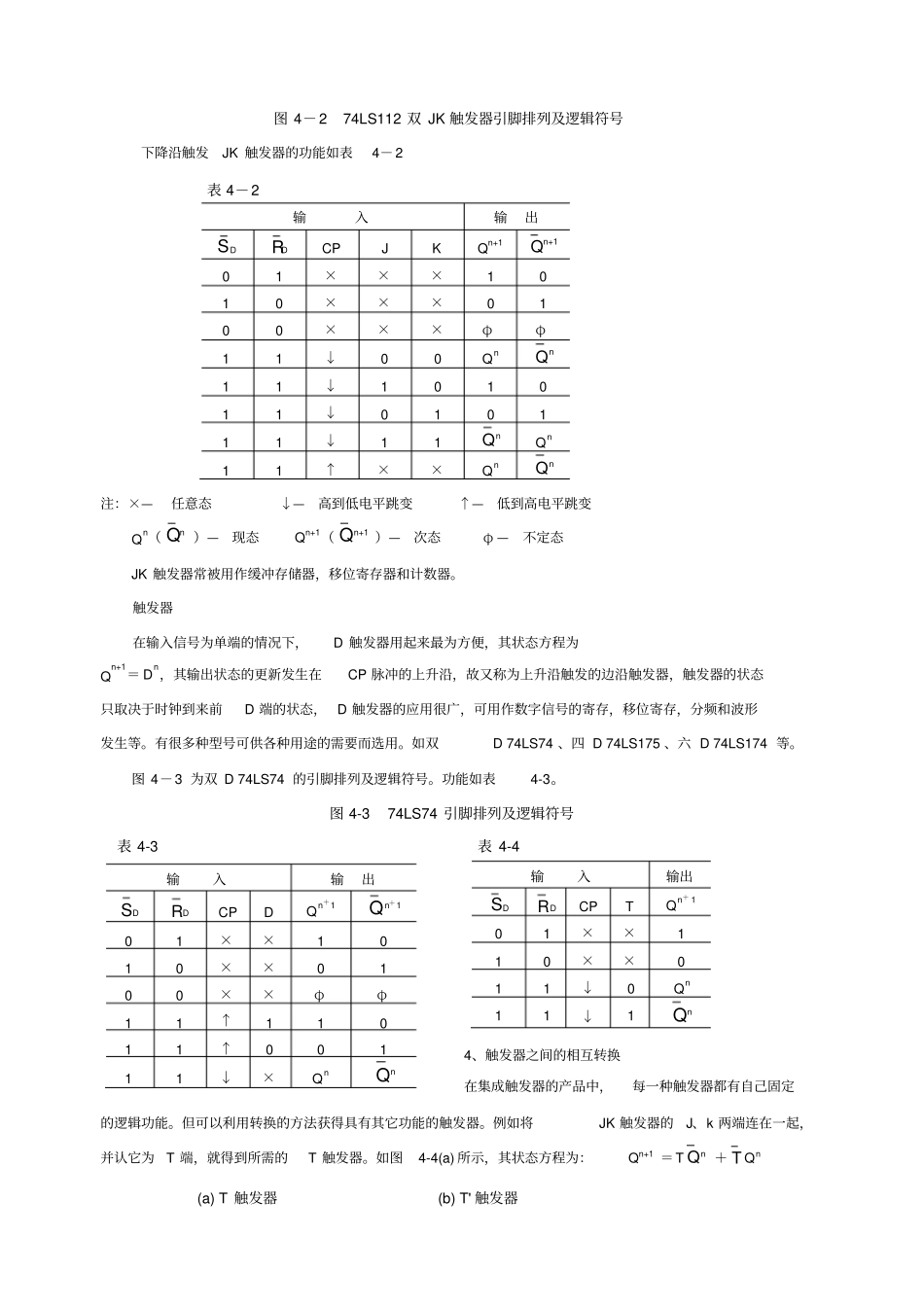

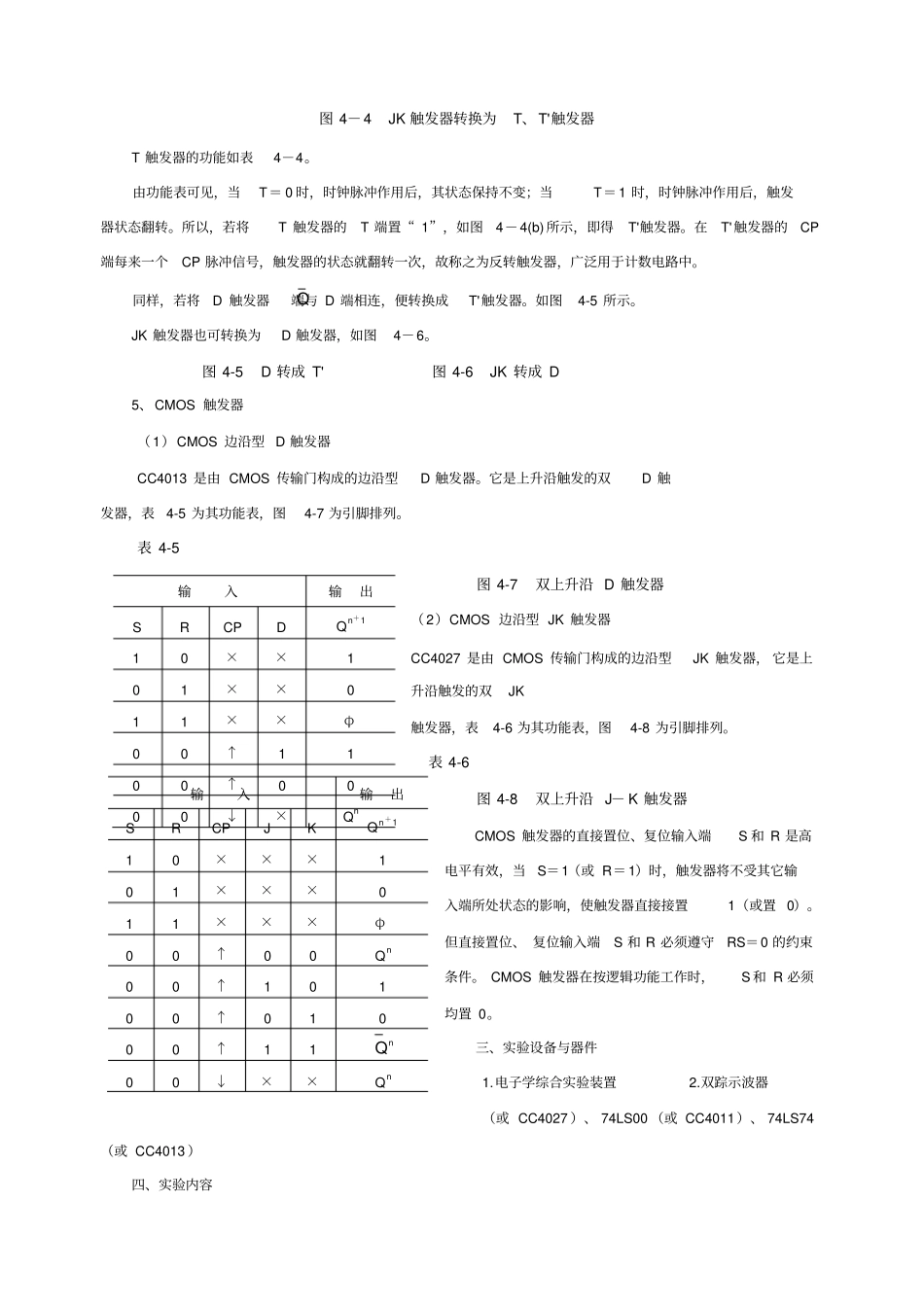

本实验采用 74LS112 双 JK 触发器,是下降边沿触发的边沿触发器

引脚功能及逻辑符号如图4-2 所示

JK 触发器的状态方程为Qn+1 =JQn+ KQnJ 和 K 是数据输入端,是触发器状态更新的依据,若J、K 有两个或两个以上输入端时,组成“与”的关系

Q与 Q 为两个互补输出端

通常把Q= 0、 Q= 1 的状态定为触发器“0”状态;而把Q=1, Q=0 定为“ 1”状态

图 4-2 74LS112 双 JK 触发器引脚排列及逻辑符号下降沿触发JK 触发器的功能如表4-2 表 4-2 输入输出SDRDCP J K Qn+1Qn+10 1 ×××1 0 1