数字电子技术实验报告学院: 数据科学与计算机学院专业:软件工程姓名: ******学号:*********日期: 2018 年 6 月 5 日实验内容:计数器的设计预习报告1数字电子技术实验报告4、异步触发器:存在触发器逐级延迟问题

同步计数器:各级触发器输出相差小,译码时能避免出现尖峰,但是电路实现较复杂

二、预习报告内容 1使用 JK 触发器设计一个 16 进制异步加法计数器,并用逻辑分析仪观察并记录 CP 和每一位的输出波形

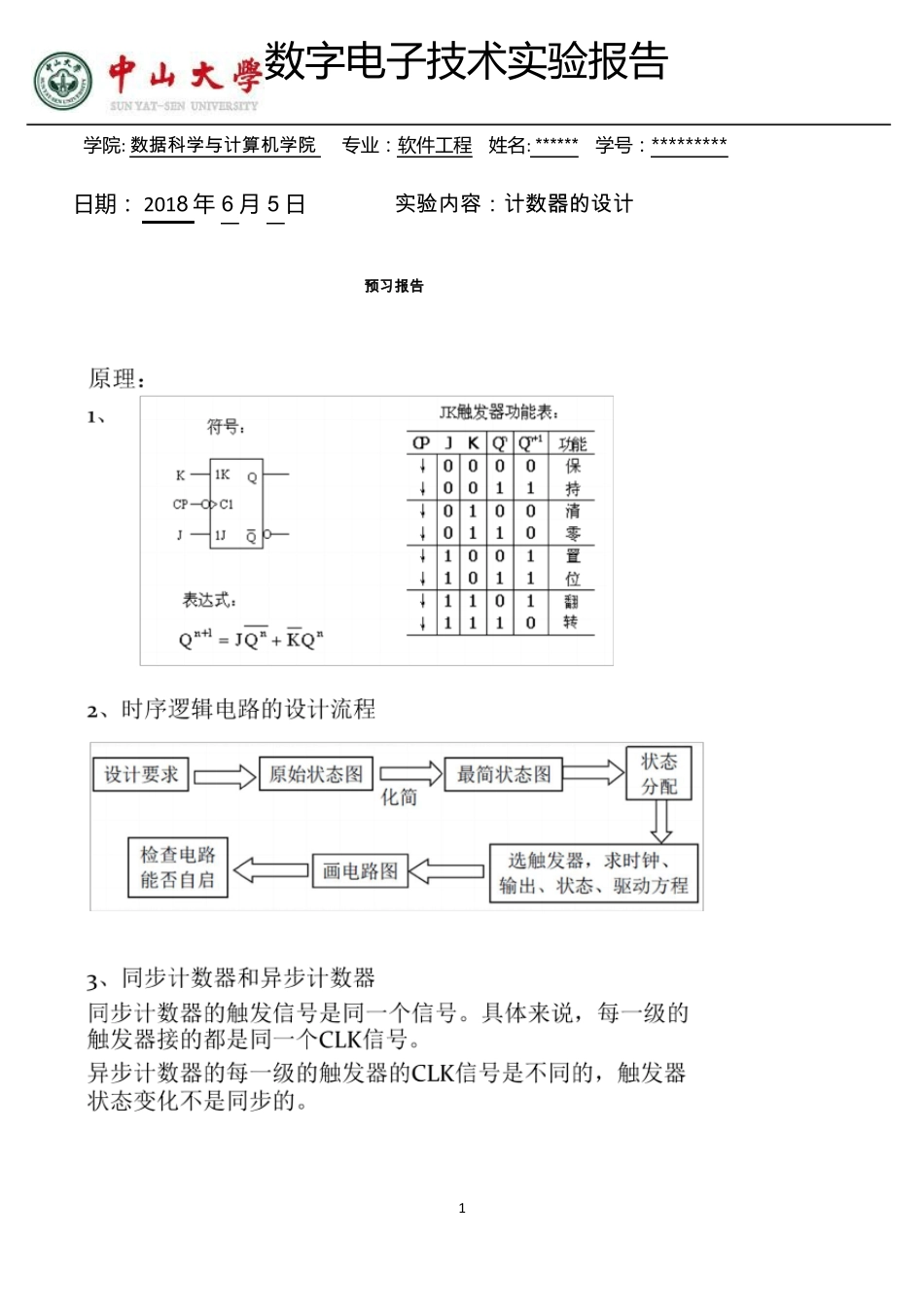

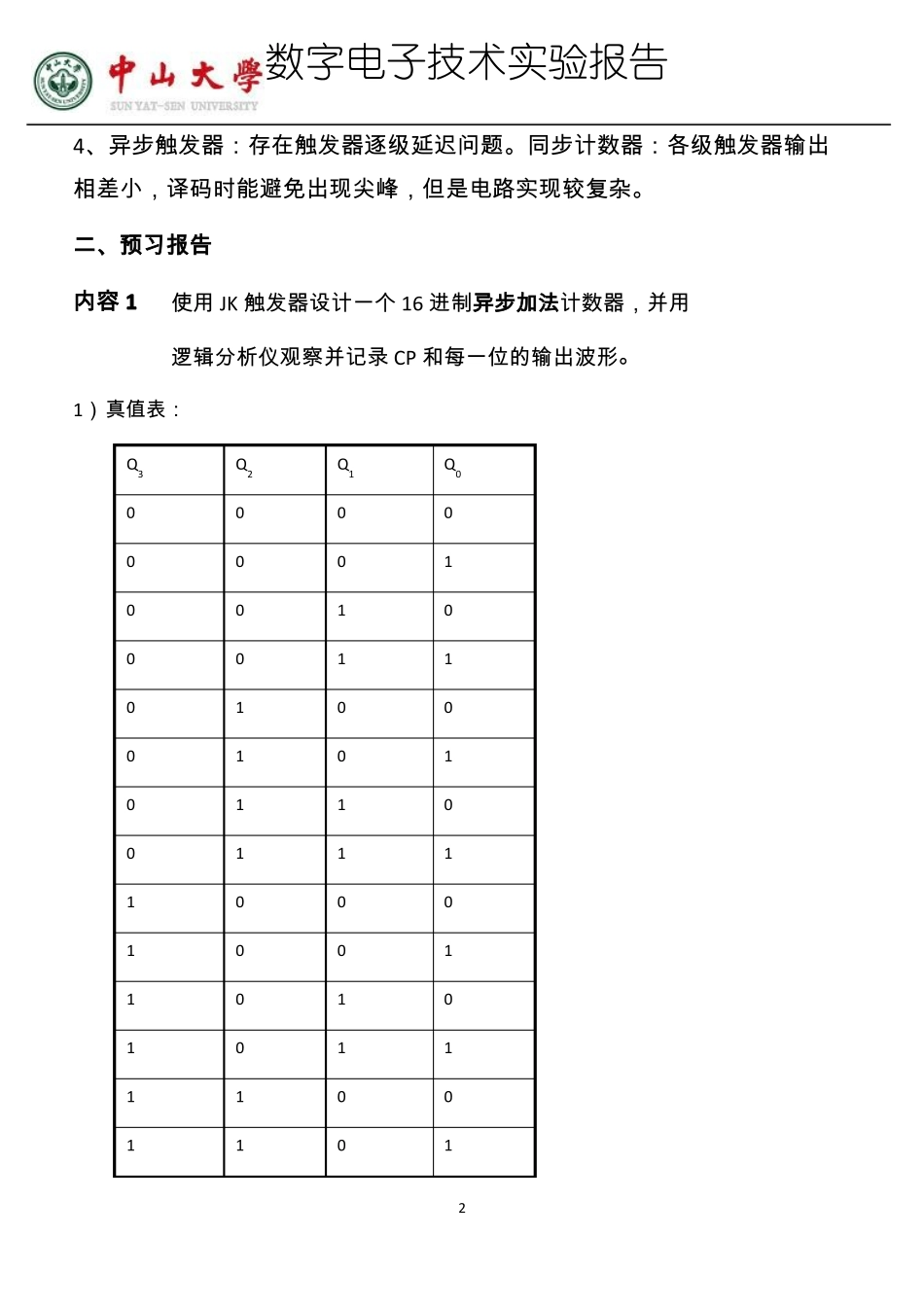

1)真值表:Q300000000111111Q200001111000011Q100110011001100Q0010101010101012数字电子技术实验报告111111012)选用 JK 触发器,控制函数:J0=K0=1J1=K1=1J2=K2=1J3=K3=1CLK 由前一个触发器的输出连接(B0 连接外部 CLK)proteus 仿真3)从左到右依次为 Q0Q1Q2Q34)波形图3数字电子技术实验报告A0 为外部 CLK,A1-A4 分别为 Q0Q1Q2Q3,成功实现

内容 2使用 JK 触发器设计一个 16 进制同步加法计数器,并用逻辑分析仪观察并记录 CP 和每一位的输出波形

1)真值表同内容 1

2)控制函数:J0=K0=1J1=K1=Q0J2=K2=Q0Q1J3=K3=Q0Q1Q2所有触发器 CLK 为同一个3)Proteus 仿真4数字电子技术实验报告4)波形图A0 为 CLK,A1-A4 分别为 Q0Q1Q2Q3内容 3使用 JK 触发器和门电路设计实现一个二进制四位计数器模仿 74LS194功能(详见实验七 表二)

要求在实验箱上设计实现左移或右移功能;在 proteus 软件上实现置零,保持,左移,右移,并行送数功能

1) 功能表2) 逻辑表达式保持:QN+1 = QN右移:Q3N+1= Q0 , Q2N+1= Q3 ,