第七章 有限状态机和可综合风格的Verilog HDL ---------------------------------------------------------------------------------------------------------------------- 1 1 4第七章 有限状态机和可综合风格的Verilog HDL 前言 由于Verilog HDL和 VHDL 行为描述用于综合的历史还只有短短的几年,可综合风格的Verilog HDL 和VHDL的语法只是它们各自语言的一个子集

又由于HDL的可综合性研究近年来非常活跃,可综合子集的国际标准目前尚未最后形成,因此各厂商的综合器所支持的HDL子集也略有所不同

本教材中有关可综合风格的Verilog HDL的内容,我们只着重介绍RTL级、算法级和门级逻辑结构的描述,而系统级(数据流级)的综合由于还不太成熟,暂不作介绍

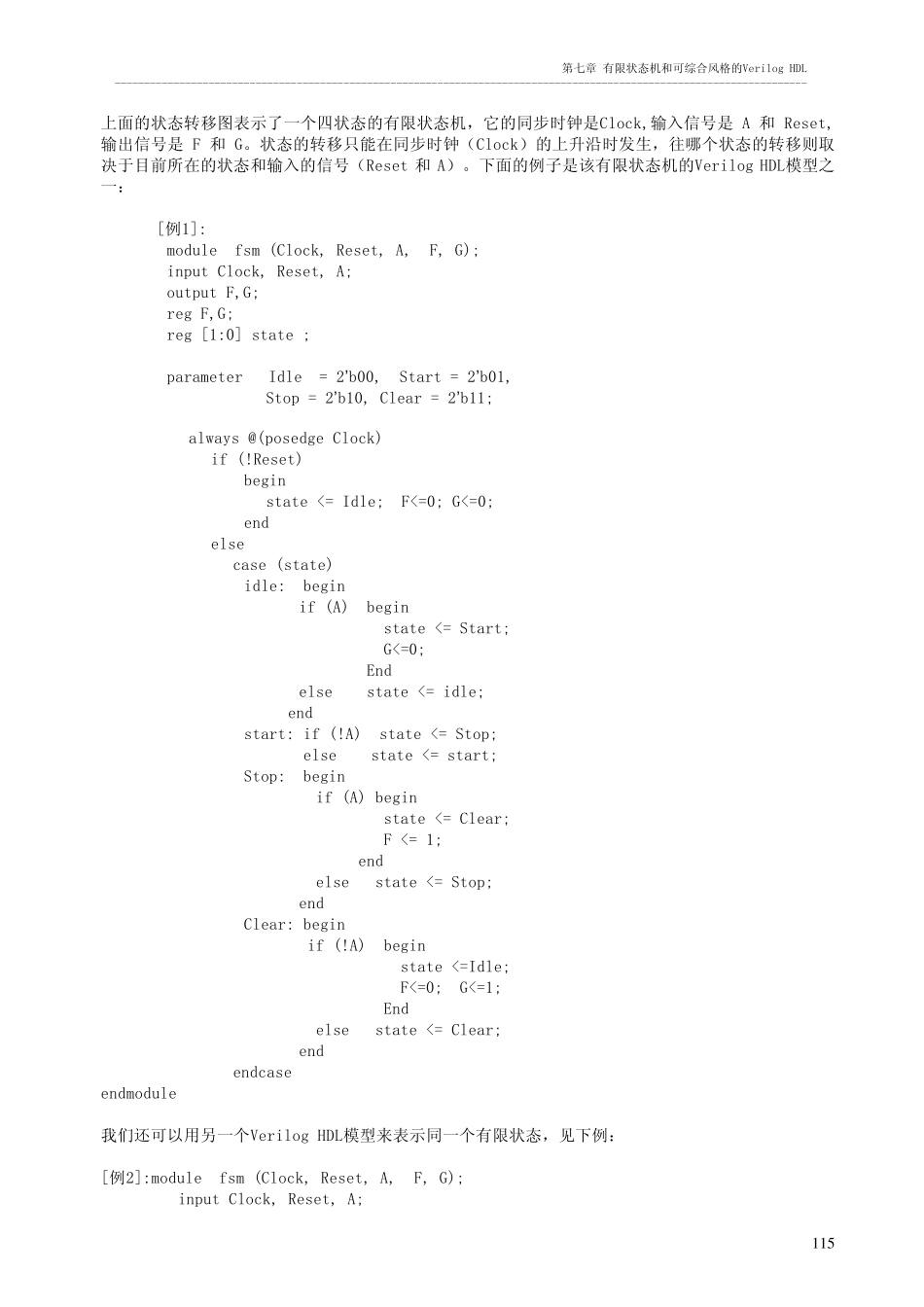

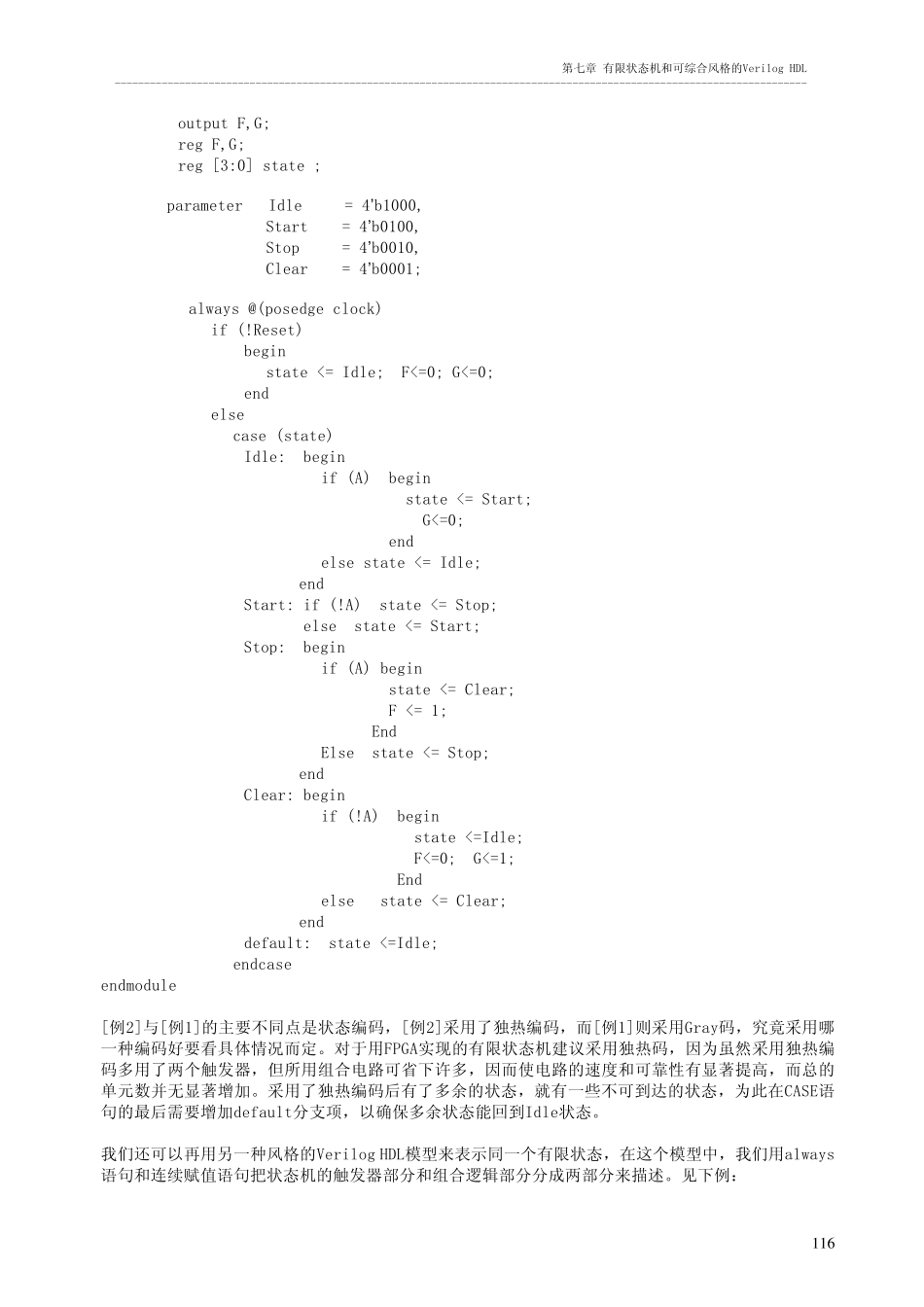

由于寄存器传输级(RTL)描述是以时序逻辑抽象所得到的有限状态机为依据的,所以把一个时序逻辑抽象成一个同步有限状态机是设计可综合风格的Verilog HDL模块的关键

在本章中我们将通过各种实例由浅入深地来介绍各种可综合风格的Verilog HDL模块,并把重点放在时序逻辑的可综合有限状态机的Verilog HDL设计要点

至于组合逻辑,因为比较简单,只需阅读典型的用Verilog HDL描述的可综合的组合逻辑的例子就可以掌握

为了更好地掌握可综合风格,还需要较深入地了解 阻 塞 和非阻 塞 赋 值 的差 别 和在不同的情 况 下 正 确 使 用这 两 种赋 值的方 法

只有深入地理 解 阻 塞 和非阻 塞 赋 值 语句 的细 微 不同,才 有可能 写 出 不仅 可以仿 真 也可以综合的Verilog HDL模块

只要按 照 一定 的原 则 来编 写 代 码 就可以保 证