基于ADF4113的锁相环电路设计仿真 一、ADF4113 的主要技术特性 ADF4113 是由一个低噪声的数字鉴频鉴相器(PDF,Phase Frequency Detector),一个精确的充电泵,一个可编程的基准分频器 R,可编程的A、B 计数器以及一个双模潜质分频器(P/P+1)组成

A(6 位)和 B(13 位)计数器与双模前置分频器(P/P+1)连接,能实现一个分频比为 N 的分频器(N=BP+A)

除此之外,14 位的基准分频器 R 允许在PFD 的输入端选择 REFin 的输入频率

ADF4113 频率合成器与外部的环路的环路滤波器和压控振荡器可以实现一个完整的锁相环路

ADF4113 的电源电压为 2

5V,独立的充电泵电源电压(VP)允许在 3V 的系统中使用外部的调谐电压,充电泵电流和反向脉冲宽度可编程

可编程双模式前置分频器,其分频器频率为 64/65,并具有 3 线式串行接口、模拟和数字锁定检测、硬件和软件控制的低功耗模式

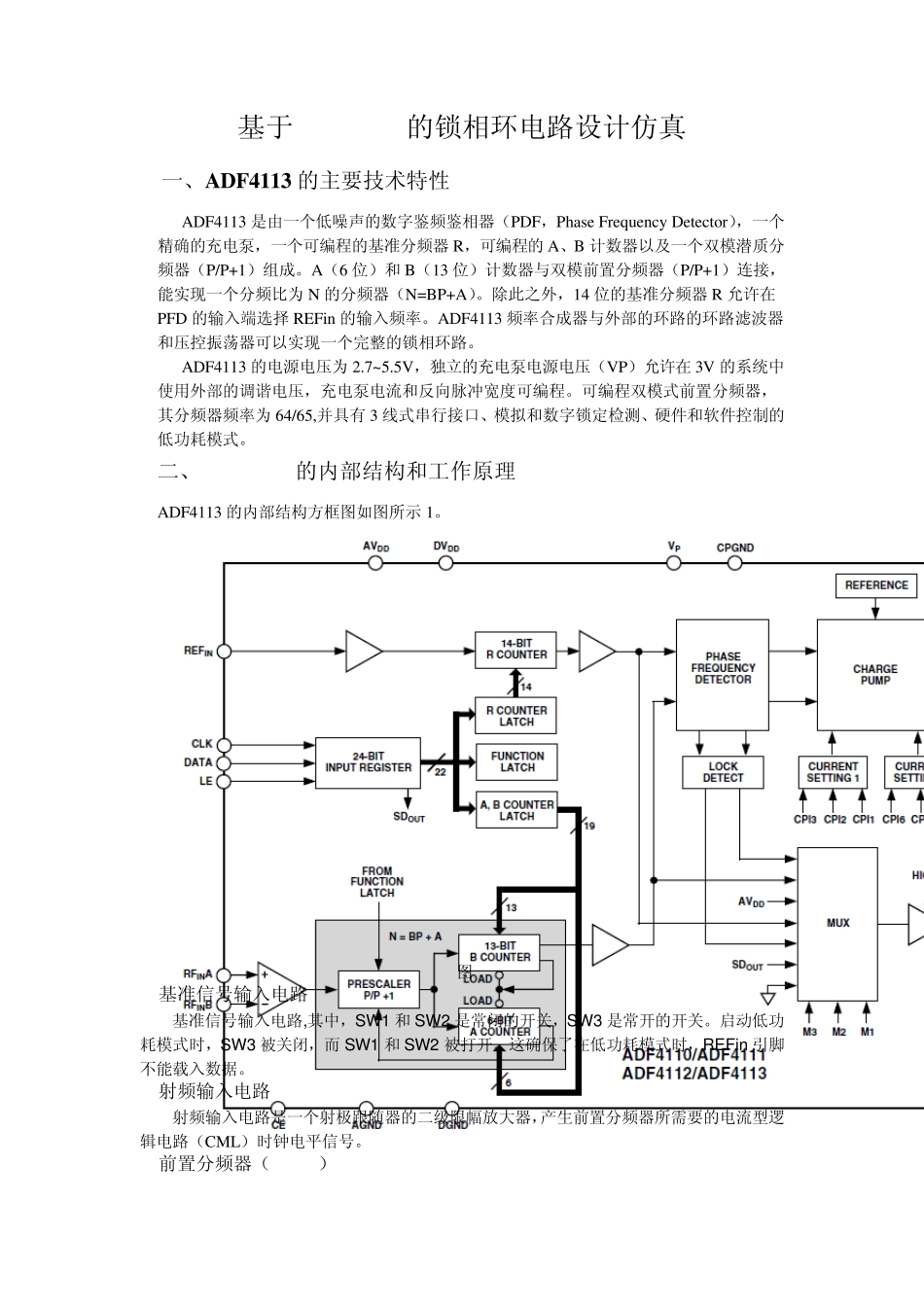

二、 ADF4113的内部结构和工作原理 ADF4113 的内部结构方框图如图所示 1

基准信号输入电路 基准信号输入电路,其中,SW1 和 SW2 是常闭的开关,SW3 是常开的开关

启动低功耗模式时,SW3 被关闭,而 SW1 和 SW2 被打开

这确保了在低功耗模式时,REFin 引脚不能载入数据

射频输入电路 射频输入电路是一个射极跟随器的二级限幅放大器,产生前置分频器所需要的电流型逻辑电路(CML)时钟电平信号

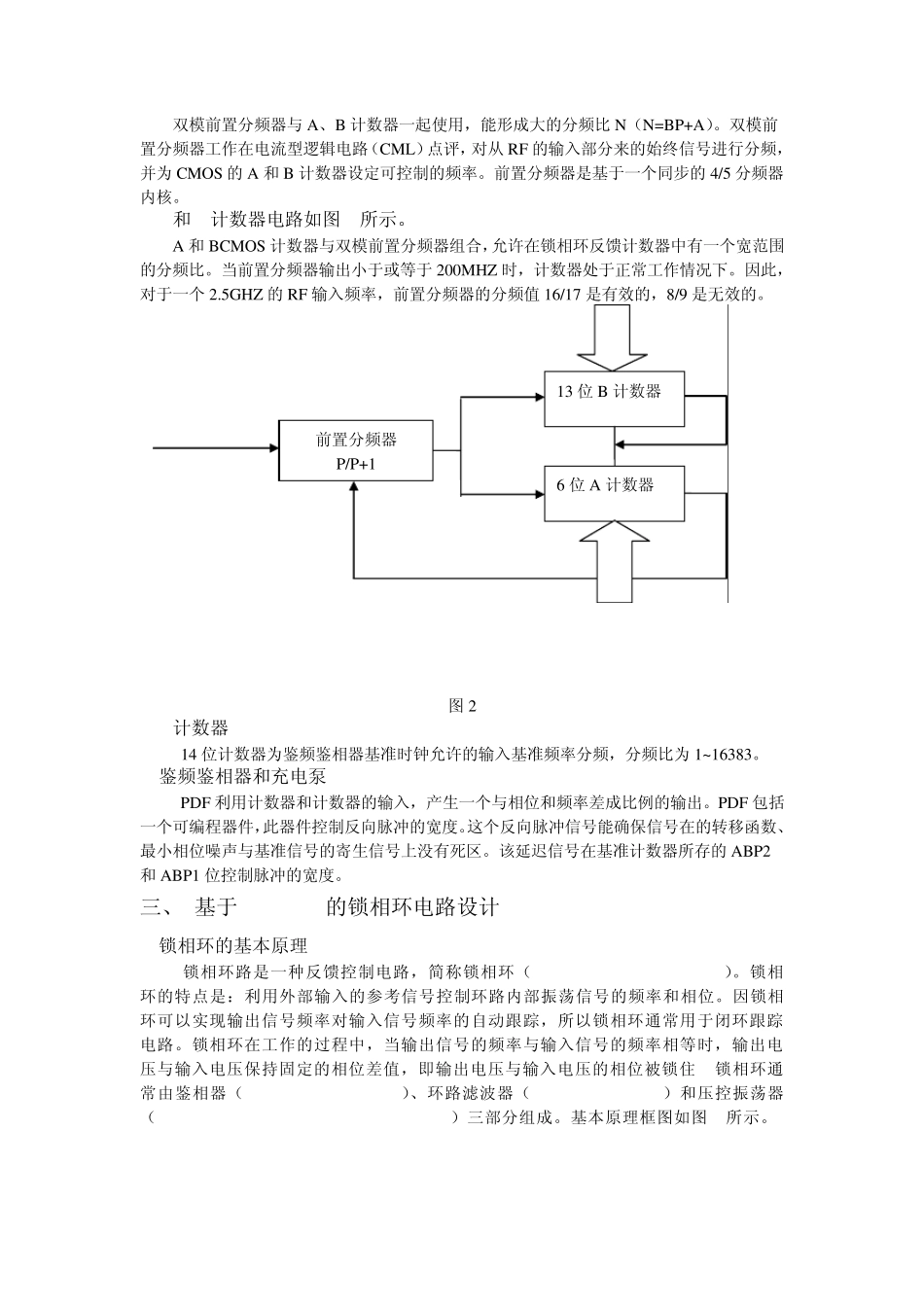

前置分频器(P/P+1) 双模前置分频器与A、B 计数器一起使用,能形成大的分频比 N(N=BP+A)

双模前置分频器工作在电流型逻辑电路(CML)点评,对从 RF 的输入部分来的始终信号进行分频,并为 CMOS 的 A 和 B 计数器设定可控制的频率

前置分频器是基于一个