Cadence 电路参数变量扫描分析 庞则桂 2006-12-22 Version-1

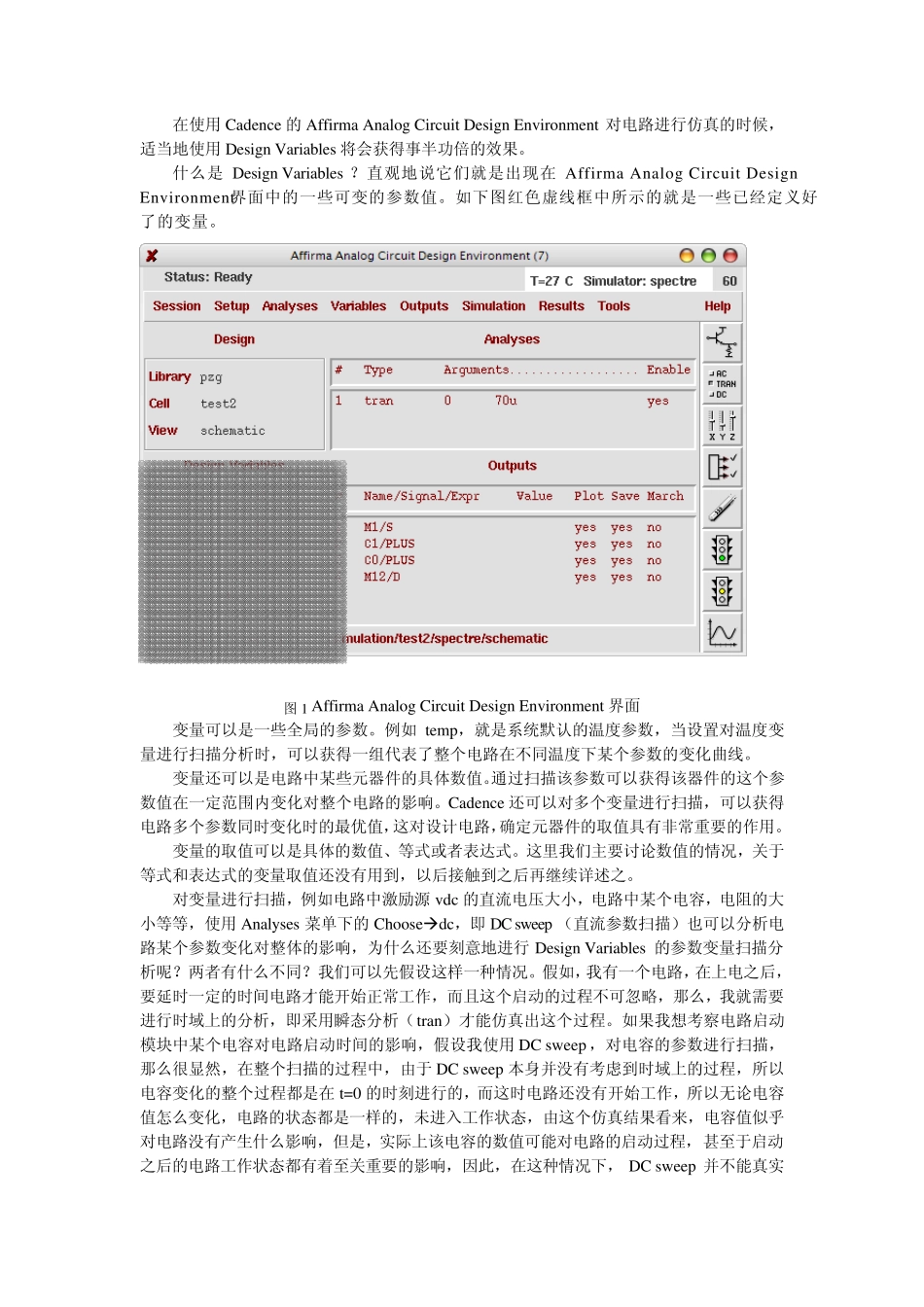

0 在使用Cadence 的Affirma Analog Circuit Design Environment 对电路进行仿真的时候,适当地使用Design Variables 将会获得事半功倍的效果

什么是Design Variables

直观地说它们就是出现在Affirma Analog Circuit Design Environment界面中的一些可变的参数值

如下图红色虚线框中所示的就是一些已经定义好了的变量

图1 Affirma Analog Circuit Design Environment 界面 变量可以是一些全局的参数

例如temp,就是系统默认的温度参数,当设置对温度变量进行扫描分析时,可以获得一组代表了整个电路在不同温度下某个参数的变化曲线

变量还可以是电路中某些元器件的具体数值

通过扫描该参数可以获得该器件的这个参数值在一定范围内变化对整个电路的影响

Cadence 还可以对多个变量进行扫描,可以获得电路多个参数同时变化时的最优值,这对设计电路,确定元器件的取值具有非常重要的作用

变量的取值可以是具体的数值、等式或者表达式

这里我们主要讨论数值的情况,关于等式和表达式的变量取值还没有用到,以后接触到之后再继续详述之

对变量进行扫描,例如电路中激励源 vdc 的直流电压大小,电路中某个电容,电阻的大小等等,使用Analyses 菜单下的Choosedc,即 DC sweep (直流参数扫描)也可以分析电路某个参数变化对整体的影响,为什么还要刻意地进行Design Variables 的参数变量扫描分析呢

两者有什么不同

我们可以先假设这样一种情况

假如,我有一个电路,在上电之后,要延时一定的时间电路才能开始正常工作,而且这个启动的过程不可忽略,那么,