3 PCB 设计建议 3

1 Fanou t封装设计建议 Hi3716M 的封装为PBGA600 ,管脚间距0

在PCB 设计时,可以采用四层PCB 板的设计,建议如下分层: TOP 层:信号走线 内一层:地平面层 内二层:电源平面层 BOTTOM 层:信号走线 在成本非常敏感的应用方案中,也可以采用二层PCB 板的设计,PCB 分层建议如下: TOP 层:信号走线和部分电源走线 BOTTOM 层:地平面层和部分电源走线 PCB 设计注意事项: 元器件布局在TOP 层,信号线尽量走TOP 层,滤波小电容可放在BOTTOM 层

电源管脚用走粗线

尽量保持BOTTOM 层为一个完整的地平面层

主芯片出线推荐过孔大小为8m il, 线宽为5m il

PCB 材料FR-4,PCB 板厚度为1

6 毫米,铜箔厚度为1 盎司,填充介质介电常数4

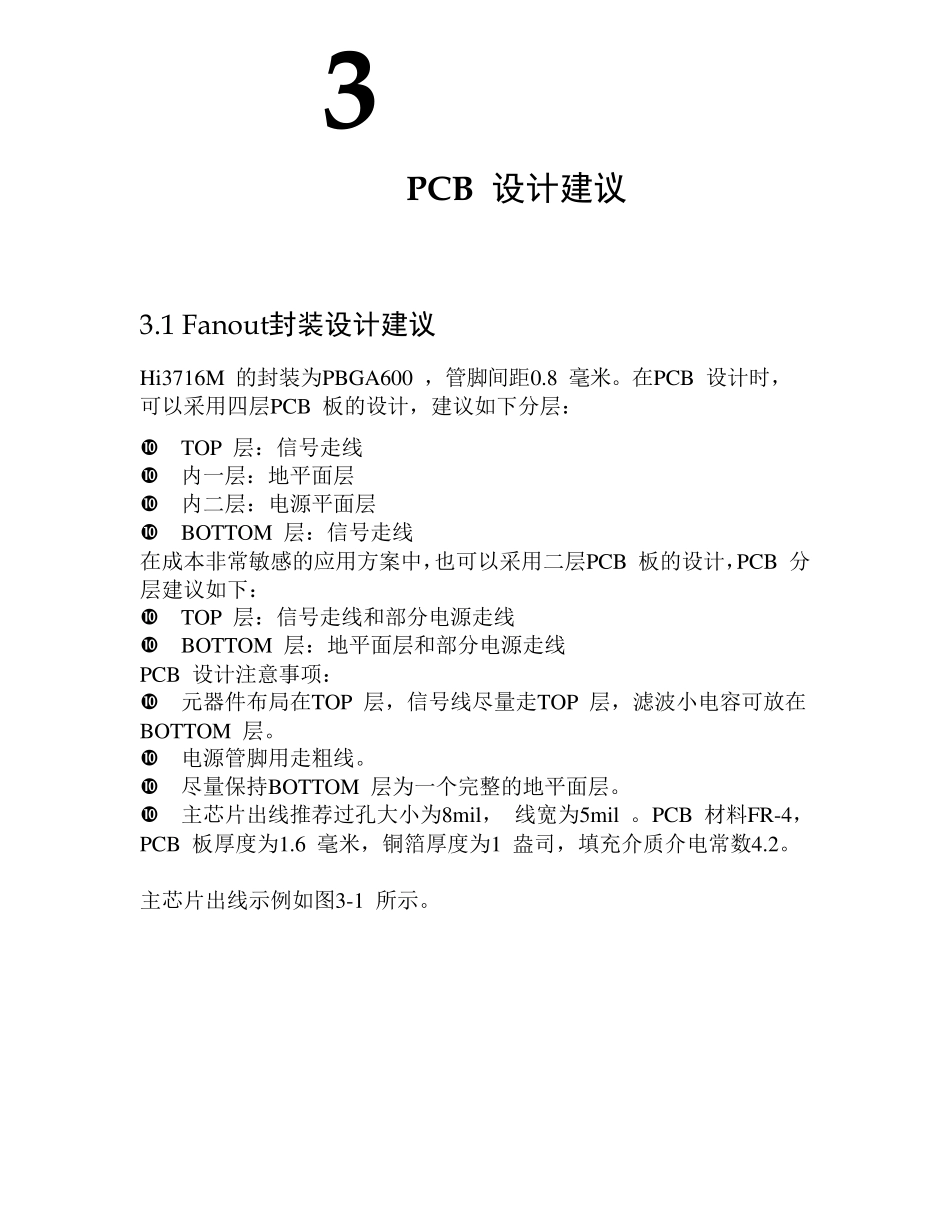

主芯片出线示例如图3-1 所示

图3-1 主芯片出线示例图 3

2 DDR SDRAM接口电路设计建议 Hi3716M 内部集成了32 位宽的DDR2//DDR3 兼容接口控制器

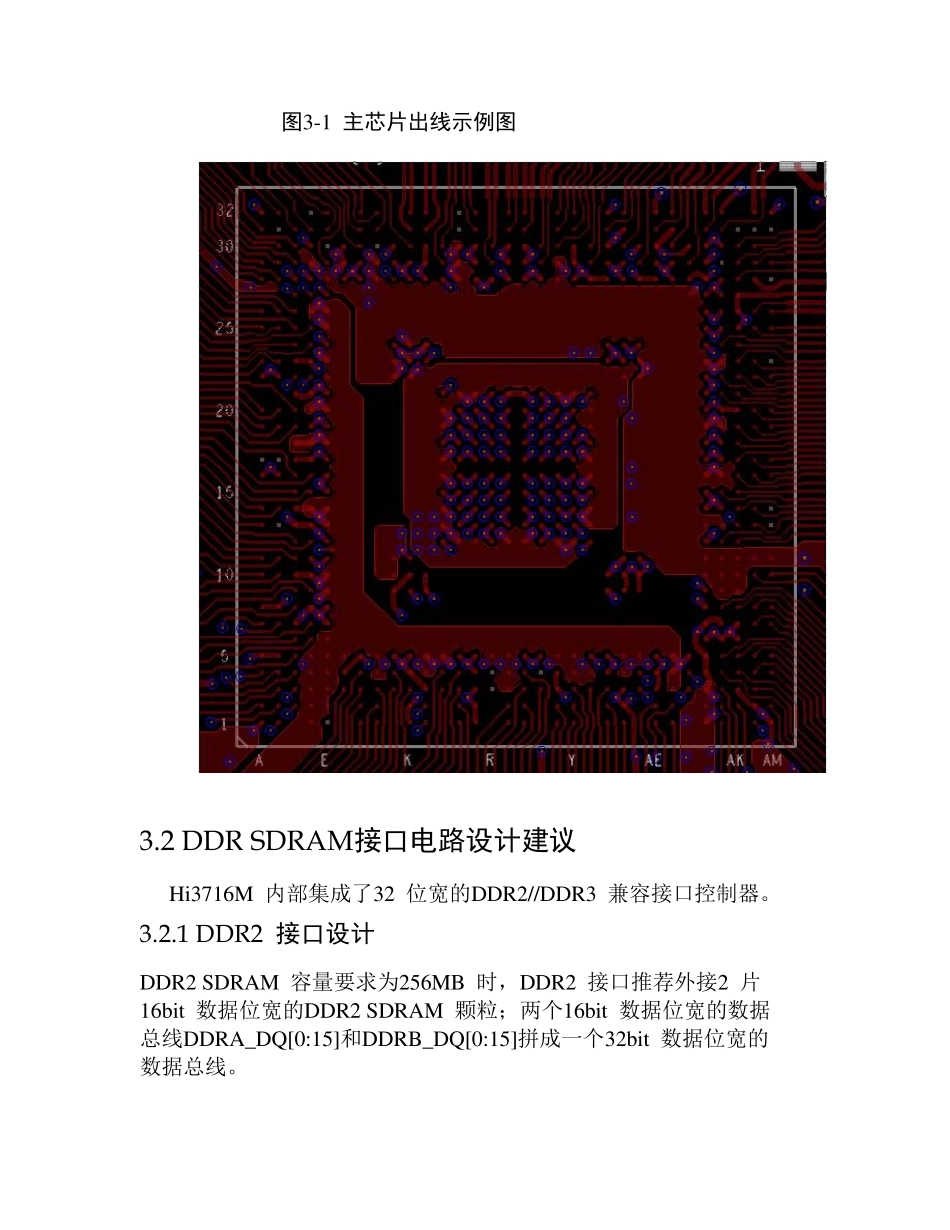

1 DDR2 接口设计 DDR2 SDRAM 容量要求为256MB 时,DDR2 接口推荐外接2 片16bit 数据位宽的DDR2 SDRAM 颗粒;两个16bit 数据位宽的数据总线DDRA_DQ[0:15]和DDRB_DQ[0:15]拼成一个32bit 数据位宽的数据总线

DDRB_DQ[0:15]对 应 32bit 位 宽 数 据 总 线 DQ[16:31]

容量要求为512MB 时,DDR2 接口推荐外接4 片8bit 位宽的DDR2 SDRAM 颗粒

外接4 片8bit 数据位宽的DDR2 颗粒时,需要采用至少4 层PCB 板的设计

外接16bit 数据位宽DDR2 SDRAM