DDR 内存布线指导,DDR Layout Guide 在现代高速数字电路的设计过程中,工程师总是不可避免的会与DDR 或者DDR2,SDRAM 打交道

DDR 的工作频率很高,因此,DDR的布线(或者Layout)也就成为了一个十分关键的问题,很多时候,DDR 的布线直接影响着信号完整性

下面本文针对 DDR 的布线问题(Layout)进行讨论

信号引脚说明 VSS 为数字地,VSSQ 为信号地,若无特别说明,两者是等效的

VDD 为器件内核供电,VDDDQ 为器件的DQ 和 I/O 供电,若无特别说明,两者是等效的

对于 DRAM 来说,定义信号组如下: • 数字信号组 DQ,DQS,xDM,其中每个字节又是内部的一个信道Lane 组,如 DQ0~DQ7,DQS,LDM 为一个信号组

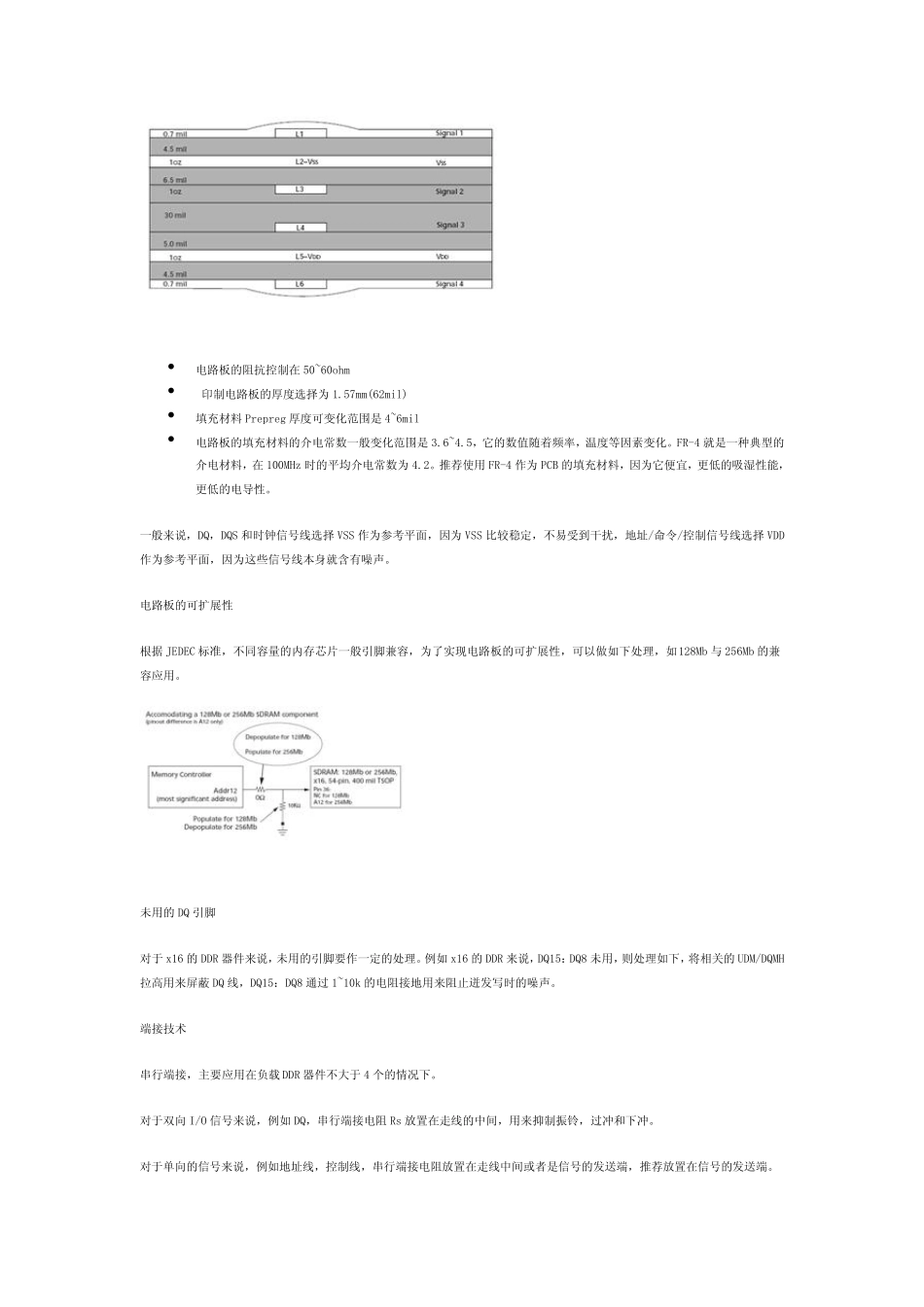

• 地址信号组:ADDRESS • 命令信号组:CAS#,RAS#,WE# • 控制信号组:CS#,CKE • 时钟信号组:CK,CK# 印制电路板叠层,PCB Stackups 推荐使用 6 层电路板,分布如下: • 电路板的阻抗控制在50~60ohm • 印制电路板的厚度选择为1

57mm(62mil) • 填充材料Prepreg 厚度可变化范围是4~6mil • 电路板的填充材料的介电常数一般变化范围是3

5,它的数值随着频率,温度等因素变化

FR-4 就是一种典型的介电材料,在100MHz 时的平均介电常数为4

推荐使用 FR-4 作为PCB 的填充材料,因为它便宜,更低的吸湿性能,更低的电导性

一般来说,DQ,DQS 和时钟信号线选择VSS 作为参考平面,因为VSS 比较稳定,不易受到干扰,地址/命令/控制信号线选择VDD作为参考平面,因为这些信号线本身就含有噪声

电路板的可扩展性 根据 JEDEC 标准,不同容量的内存芯片一般引脚兼容,为了实现电路板的可扩