DDR I/II总线的仿真分析方法 DDR 总线概览 DDR全名为Double Data Rate SDRAM ,简称为DDR

现在市场上的DDR已经发展到了DDR II,速度可以支持到667MT/s

FBD(Fully Buffered DIMM)也即将在市场上推出,速度更快

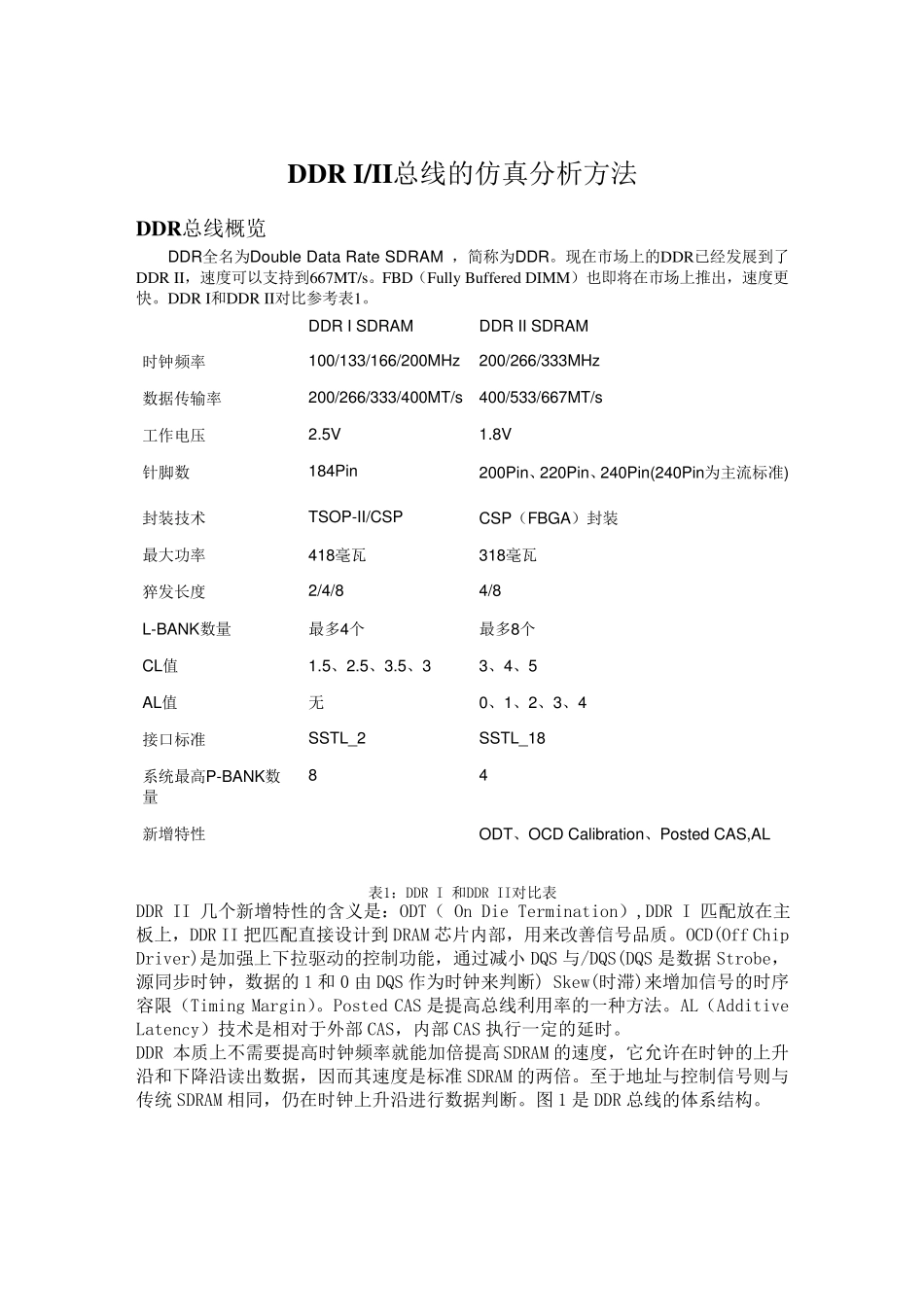

DDR I和DDR II对比参考表1

DDR I SDRAM DDR II SDRAM 时钟频率 100/133/166/200MHz 200/266/333MHz 数据传输率 200/266/333/400MT/s 400/533/667MT/s 工作电压 2

8V 针脚数 184Pin 200Pin、220Pin、240Pin(240Pin为主流标准) 封装技术 TSOP-II/CSP CSP(FBGA)封装 最大功率 418毫瓦 318毫瓦 猝发长度 2/4/8 4/8 L-BANK数量 最多4个 最多8个 CL值 1

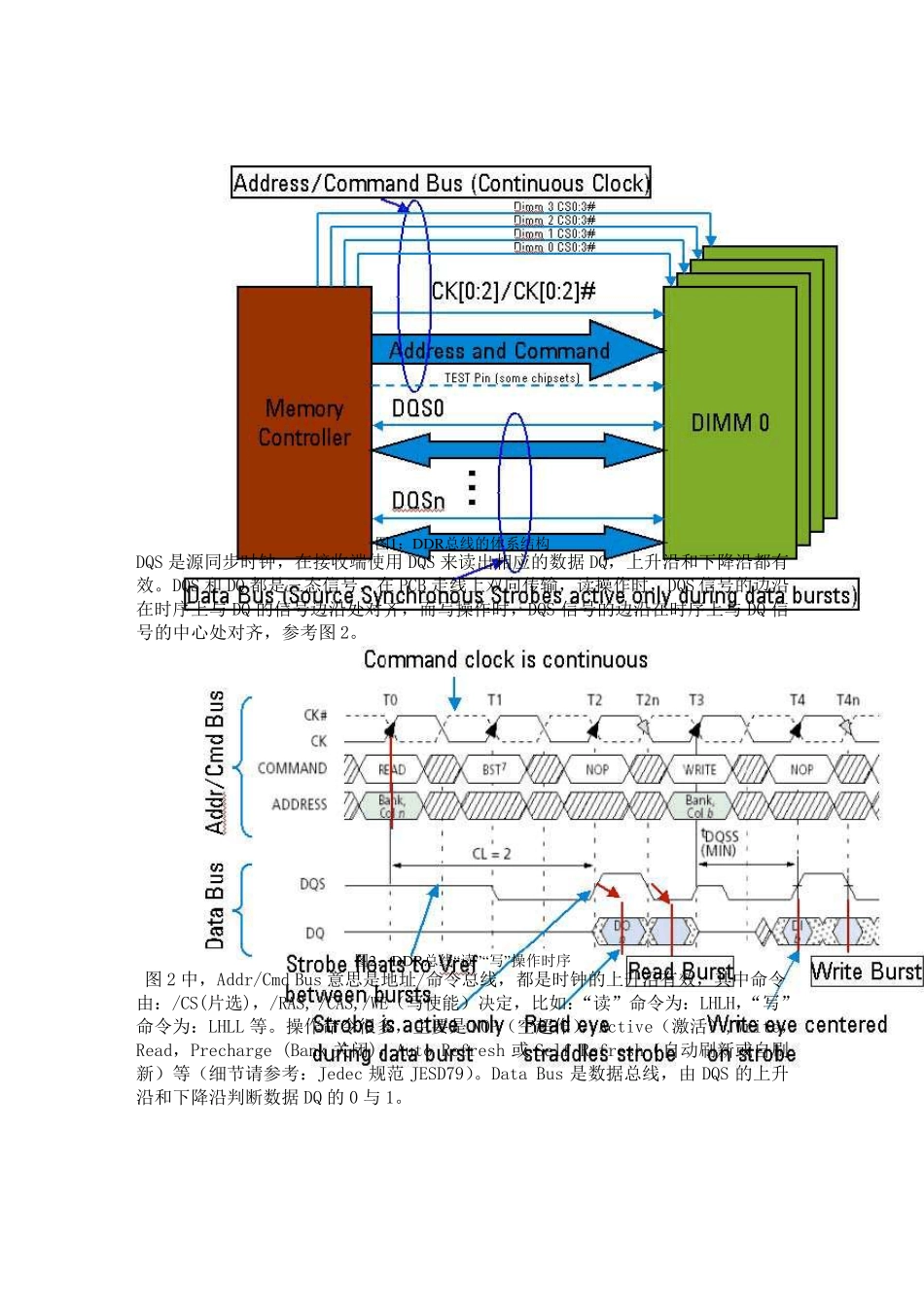

5、3 3、4、5 AL值 无 0、1、2、3、4 接口标准 SSTL_2 SSTL_18 系统最高P-BANK数量 8 4 新增特性 ODT、OCD Calibration、Posted CAS,AL 表1:DDR I 和DDR II对比表 DDR II 几个新增特性的含义是:ODT( On Die Termination),DDR I 匹配放在主板上,DDR II 把匹配直接设计到DRAM 芯片内部,用来改善信号品质

OCD(Off Chip Driver)是加强上下拉驱动的控制功能,通过减小DQS 与/DQS(DQS 是数据Strobe,源同步时钟,数据的1 和0 由DQS 作为时钟来判断) Skew(时滞)来增加信号的时序容限(Timing Margin)

Posted CAS 是提高总线利用率的一种方法

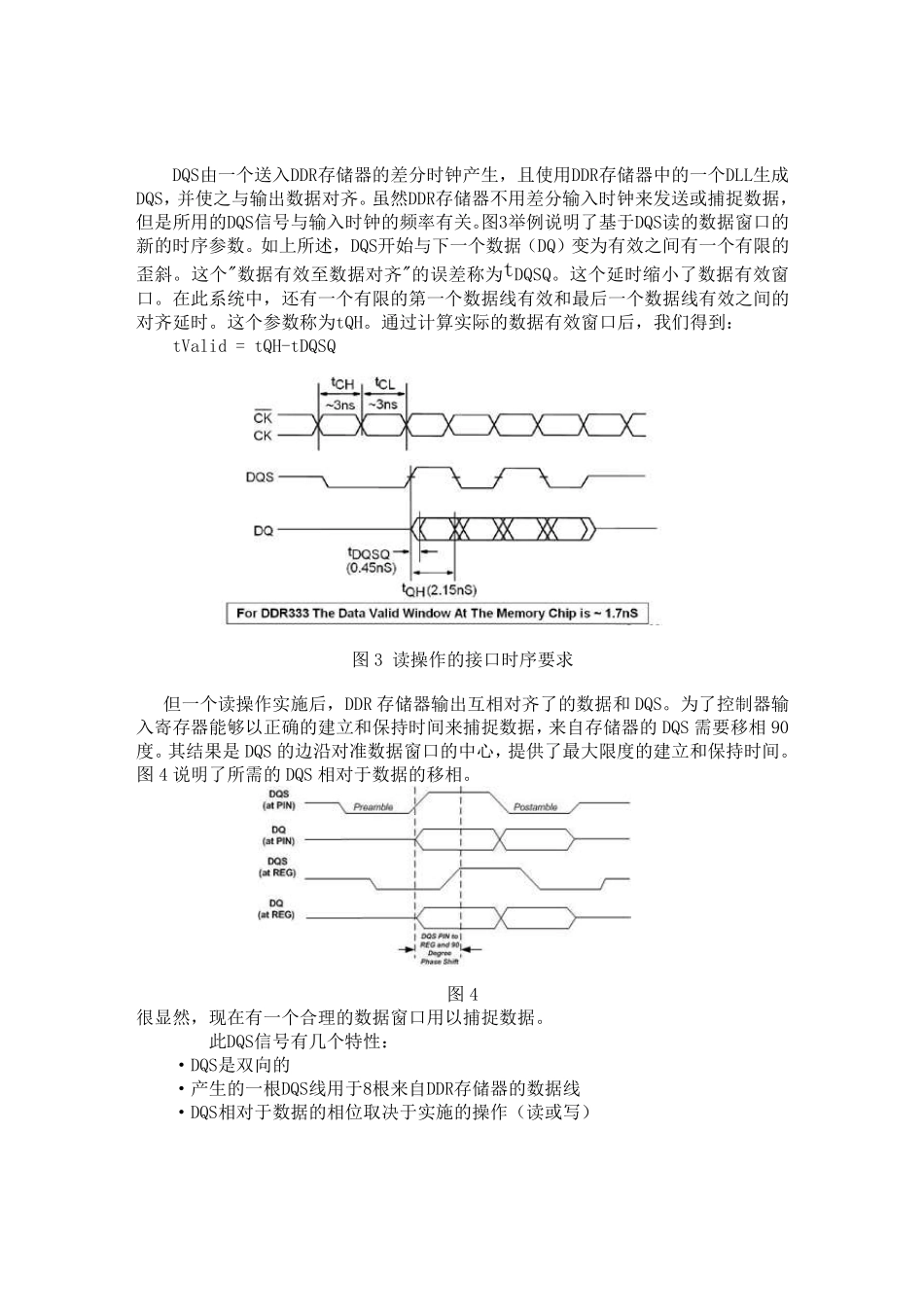

AL(Additive Latenc