DSP 第二次大作业 一、详细描述F240,F2812 芯片引脚的符号与功能

1、TMS320F240 芯片引脚与功能 TMS320F240 为TI 公司所出品的定点式数字信号处理器芯片,具有强大的外围(64k I/O space、10 bit A/D Converter、Digital I/O peripheral) ,芯片内部采用了加强型哈佛架构(Enhanced Harvard Architecture),由三个平行处理的总线─程序地址总线(PAB)、数据读出地址总线(DRAB)及数据写入地址总线(DWAB),使其能进入多个内存空间

由于总线之操作各自独立,因此可同时进入程序及数据存储器空间,而两内存间的数据亦可互相交换,使得其具有快速的运算速度,几乎所有的指令皆可在 50ns 周期时间内执行完毕,内部的程控以管线式的方式操作(Pipeline operation),且使用内存映像的方式,使其整体的效能可达到 20MIPS,因此非常适用于实时运转控制,而对于速度较慢的外围亦提供了w ait-states 的功能

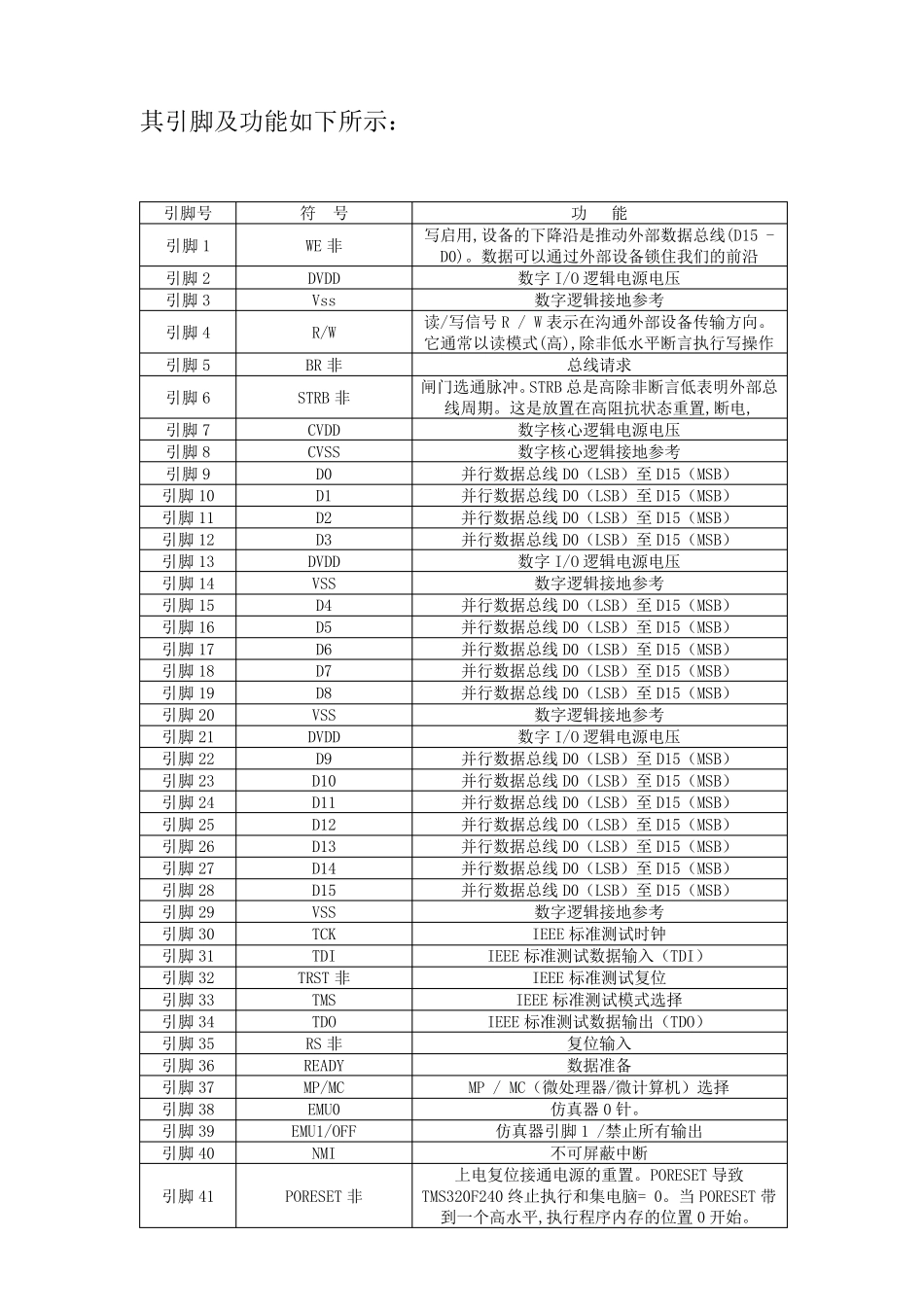

其引脚及功能如下所示: 引脚号 符 号 功 能 引脚1 WE 非 写启用,设备的下降沿是推动外部数据总线(D15 - D0)

数据可以通过外部设备锁住我们的前沿 引脚2 DVDD 数字 I/O 逻辑电源电压 引脚3 Vss 数字逻辑接地参考 引脚4 R/W 读/写信号R / W 表示在沟通外部设备传输方向

它通常以读模式(高),除非低水平断言执行写操作 引脚5 BR 非 总线请求 引脚6 STRB 非 闸门选通脉冲

STRB 总是高除非断言低表明外部总线周期

这是放置在高阻抗状态重置,断电, 引脚7 CVDD 数字核心逻辑电源电压 引脚8 CVSS 数字核心逻辑接地参考 引脚9 D0 并行数据总线D0(LSB)至 D15(MSB) 引脚10 D1 并行数据