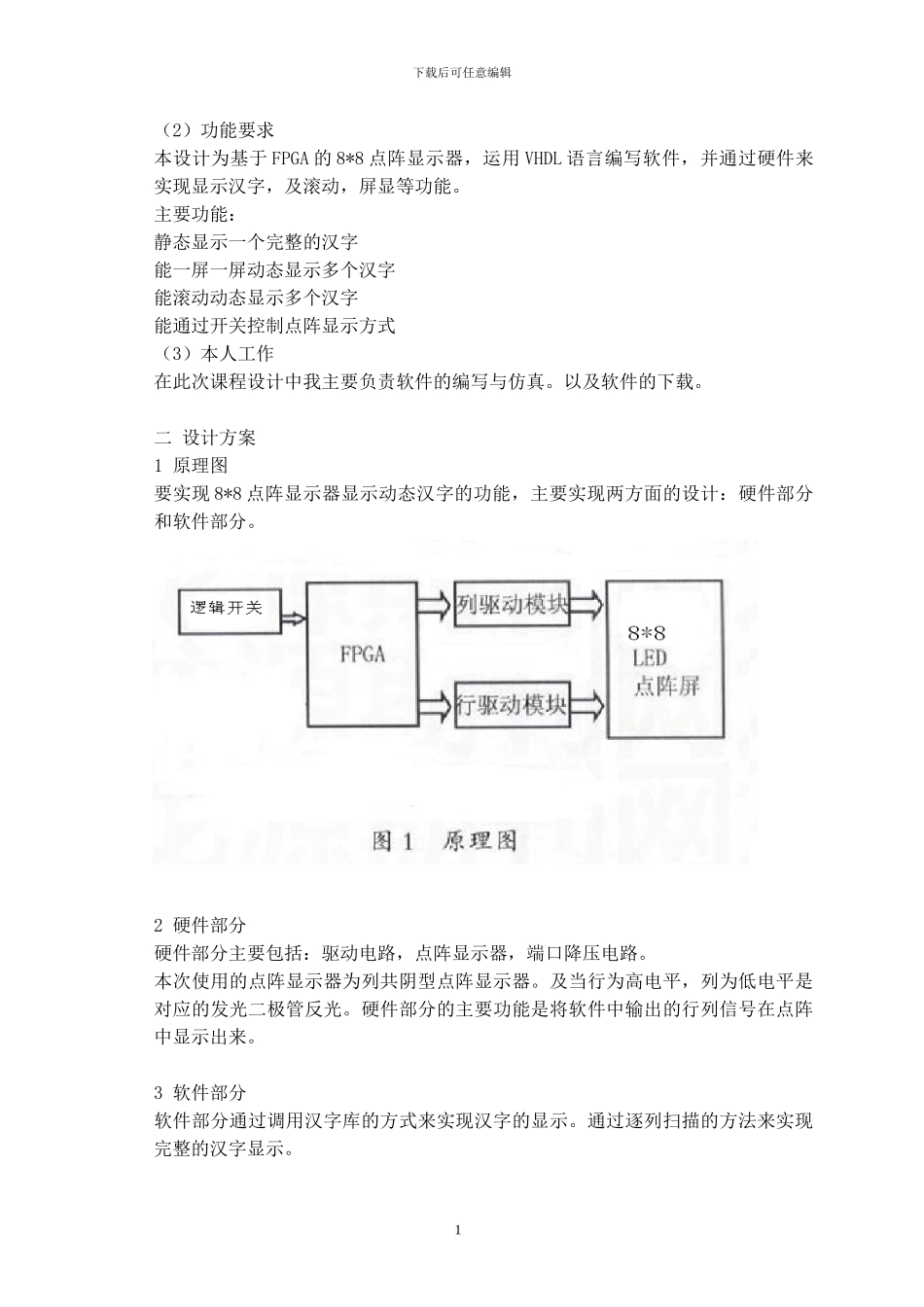

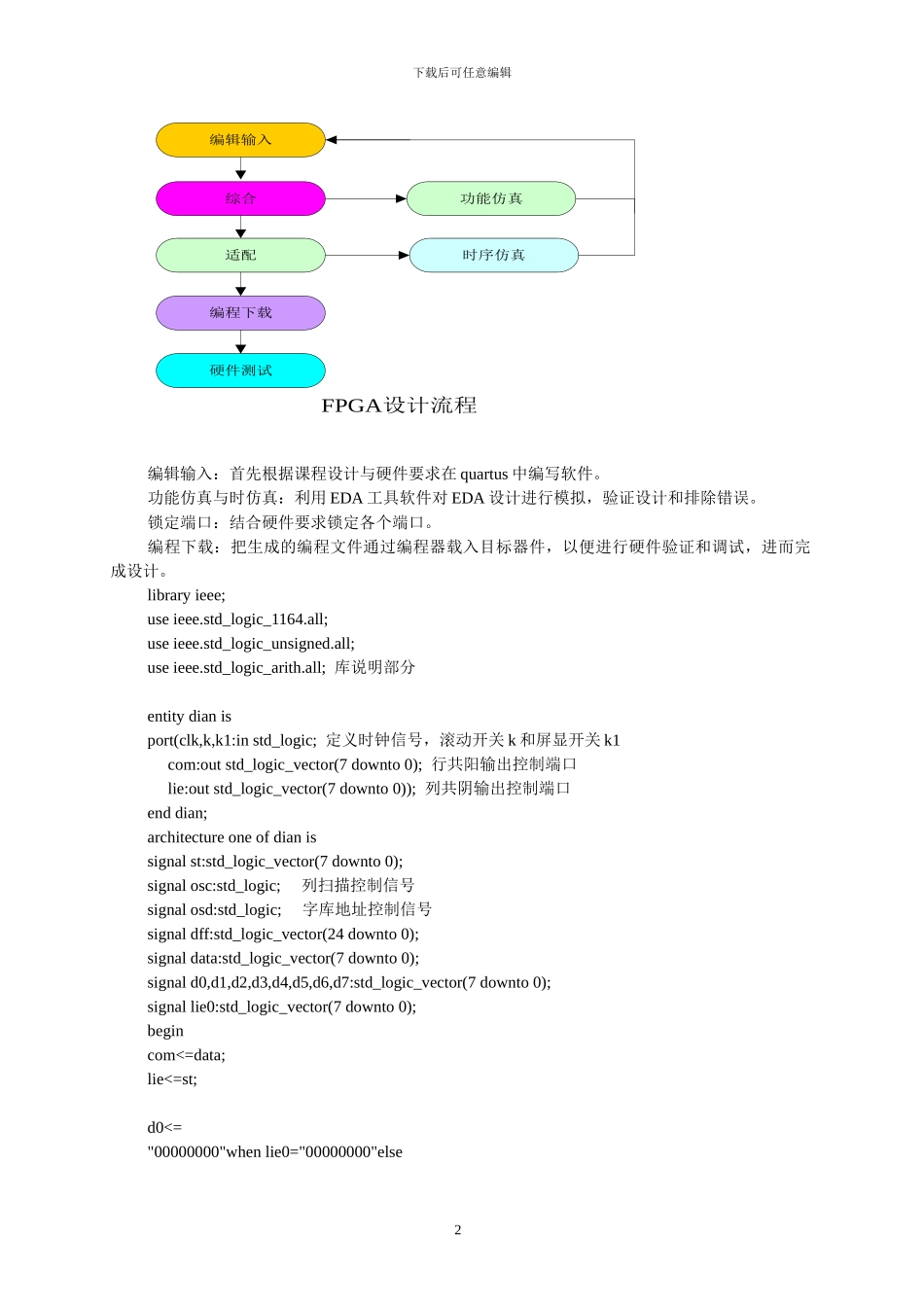

基于 FPGA 的 8*8 点阵显示器 学院名称: 电 信 学 院 专 业: 电气工程及其自动化专业 班 级: 08 电气 2 姓 名: 韩 韬 同组姓名: 董 立 峰 学 号: 08312218 指导老师姓名: 宋伟 黄成 2024 年 12 月 一 课题要求(1)技术要求①掌握较复杂逻辑的设计,调试。②掌握用 VHDL 语言设计数字逻辑电路。③掌握 quartusII6.0 软件的使用方法。④了解 8*8 列共阴点阵显示器的工作原理和功能。⑤掌握常用驱动电路的原理及使用方法。⑥掌握 EP2C5T144C8 芯片的使用。JIANGSU TEACHERS UNIVERSITY OF TECHNOLOGY 数 字 电 路 课 程 设 计 报 告下载后可任意编辑(2)功能要求本设计为基于 FPGA 的 8*8 点阵显示器,运用 VHDL 语言编写软件,并通过硬件来实现显示汉字,及滚动,屏显等功能。主要功能:静态显示一个完整的汉字能一屏一屏动态显示多个汉字能滚动动态显示多个汉字能通过开关控制点阵显示方式(3)本人工作在此次课程设计中我主要负责软件的编写与仿真。以及软件的下载。二 设计方案1 原理图要实现 8*8 点阵显示器显示动态汉字的功能,主要实现两方面的设计:硬件部分和软件部分。2 硬件部分硬件部分主要包括:驱动电路,点阵显示器,端口降压电路。本次使用的点阵显示器为列共阴型点阵显示器。及当行为高电平,列为低电平是对应的发光二极管反光。硬件部分的主要功能是将软件中输出的行列信号在点阵中显示出来。3 软件部分软件部分通过调用汉字库的方式来实现汉字的显示。通过逐列扫描的方法来实现完整的汉字显示。1下载后可任意编辑编辑输入综合适配编程下载硬件测试功能仿真时序仿真FPGA设计流程编辑输入:首先根据课程设计与硬件要求在 quartus 中编写软件。功能仿真与时仿真:利用 EDA 工具软件对 EDA 设计进行模拟,验证设计和排除错误。锁定端口:结合硬件要求锁定各个端口。编程下载:把生成的编程文件通过编程器载入目标器件,以便进行硬件验证和调试,进而完成设计。library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all; 库说明部分entity dian isport(clk,k,k1:in std_logic; 定义时钟信号,滚动开关 k 和屏显开关 k1 com:out std_logic_vector(7 downto 0); 行共阳输出控制端口 lie:out std_logic_vector(7 downto 0)); 列共阴输出控制端口end dian;architecture on...