下载后可任意编辑VHDL 抢答器的设计设计要求:1

抢答器同时供 N 名选手,(此处假设 4 个)分别用 4 个按钮 S0~ S3 表示

设置一个系统“开始复位”开关 S,该开关由主持人控制(当主持人按下该开关后以前的状态复位并且开始计时抢答)

3.抢答器具有锁存与显示功能

即选手按动按钮,锁存相应的编号,并在 LED 数码管上显示,同时扬声器发出报警声响提示

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止

抢答器具有定时抢答功能,且一次抢答的时间(0-99S)

当主持人启动“开始复位”键后,定时器进行减计时

假如定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示 00

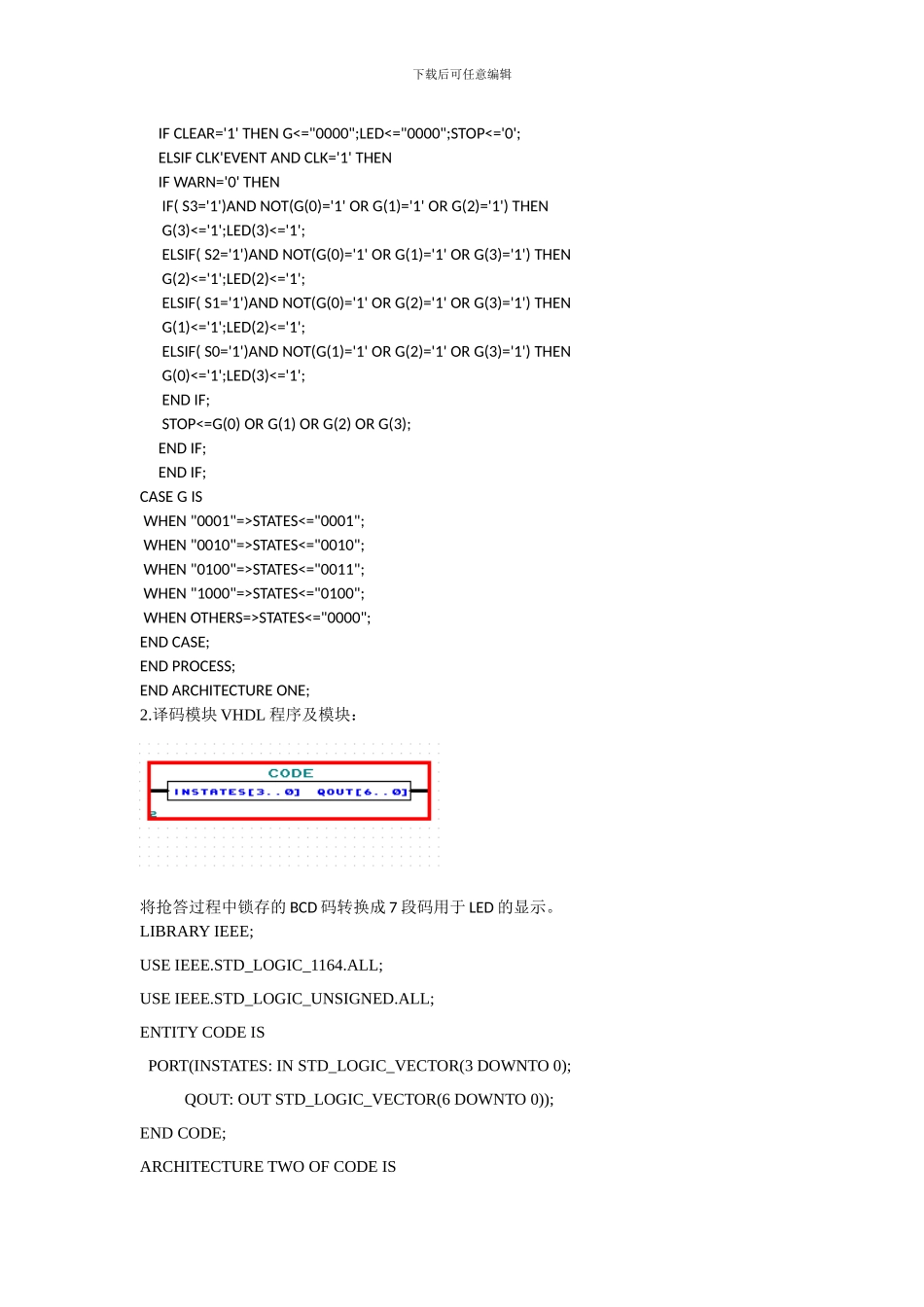

一、概述 抢答器的逻辑结构主要由抢答鉴别 lock 模块、定时模块、译码模块和报警器模块组成

在整个抢答器中最关键的是如何实现抢答封锁,在控制键按下的同时计数器倒计时显示有效剩余时间

除此之外,整个抢答器还需有一个“复位开始”信号,以便抢答器能实现清零和开始

抢答器共有 3 个输出显示,选手代号、计数器的个位和十位,他们输出全都为 BCD 码输出,这样便于和显示译码器连接

当主持人按下控制键、选手按下抢答键蜂鸣器短暂响起

二、方案设计与论证嘿嘿

将该任务分成 N 个模块进行设计,分别为:抢答器鉴别模块、抢答器计时模块、译码模块、报警模块,最后是综合

抢答器鉴别模块:在这个模块中主要实现抢答过程中的抢答功能,并且能实现当有一路抢答按键按下时,该路抢答信号将其余个绿抢答封锁的功能

在这个模块输入端有 WARN 输入(以时间控制系统的 WARN 输出信号为信号源)、一个和“时间控制系统”公用的 CLEAR 端、4 人抢答输入信号端 S0,S1,S2,S3 和有一个时钟信号端 CLK,这个时钟信号是个高频信号,用以扫描S0,S1,S2,S3 是否