Altiu m Designer 中进行信号完整性分析 Altiu m Designer的信号完整性分析功能 在高速数字系统中,由于脉冲上升/下降时间通常在10 到几百p 秒,当受到诸如内连、传输时延和电源噪声等因素的影响,从而造成脉冲信号失真的现象; 在自然界中,存在着各种各样频率的微波和电磁干扰源,可能由于很小的差异导致高速系统设计的失败; 在电子产品向高密和高速电路设计方向发展的今天,解决一系列信号完整性的问题,成为当前每一个电子设计者所必须面对的问题

业界通常会采用在PCB 制板前期,通过信号完整性分析工具尽可能将设计风险降到最低,从而也大大促进了 EDA 设计工具的发展…… 信号完整性(Signal Integrity,简称 SI)问题是指高速数字电路中,脉冲形状畸变而引发的信号失真问题,通常由传输线不阻抗匹配产生的问题

而影响阻抗匹配的因素包括信号源的架构、输出阻抗(output impedance)、走线的特性阻抗、负载端的特性、走线的拓朴(topology)架构等

解决的方式可以采用端接(termination)与调整走线拓朴的策略

信号完整性问题通常不是由某个单一 因素导致的,而是板级设计中多种因素共同作用的结果

信号完整性问题主要表现形式包括信号反射、信号振铃、地弹、串扰等; 1

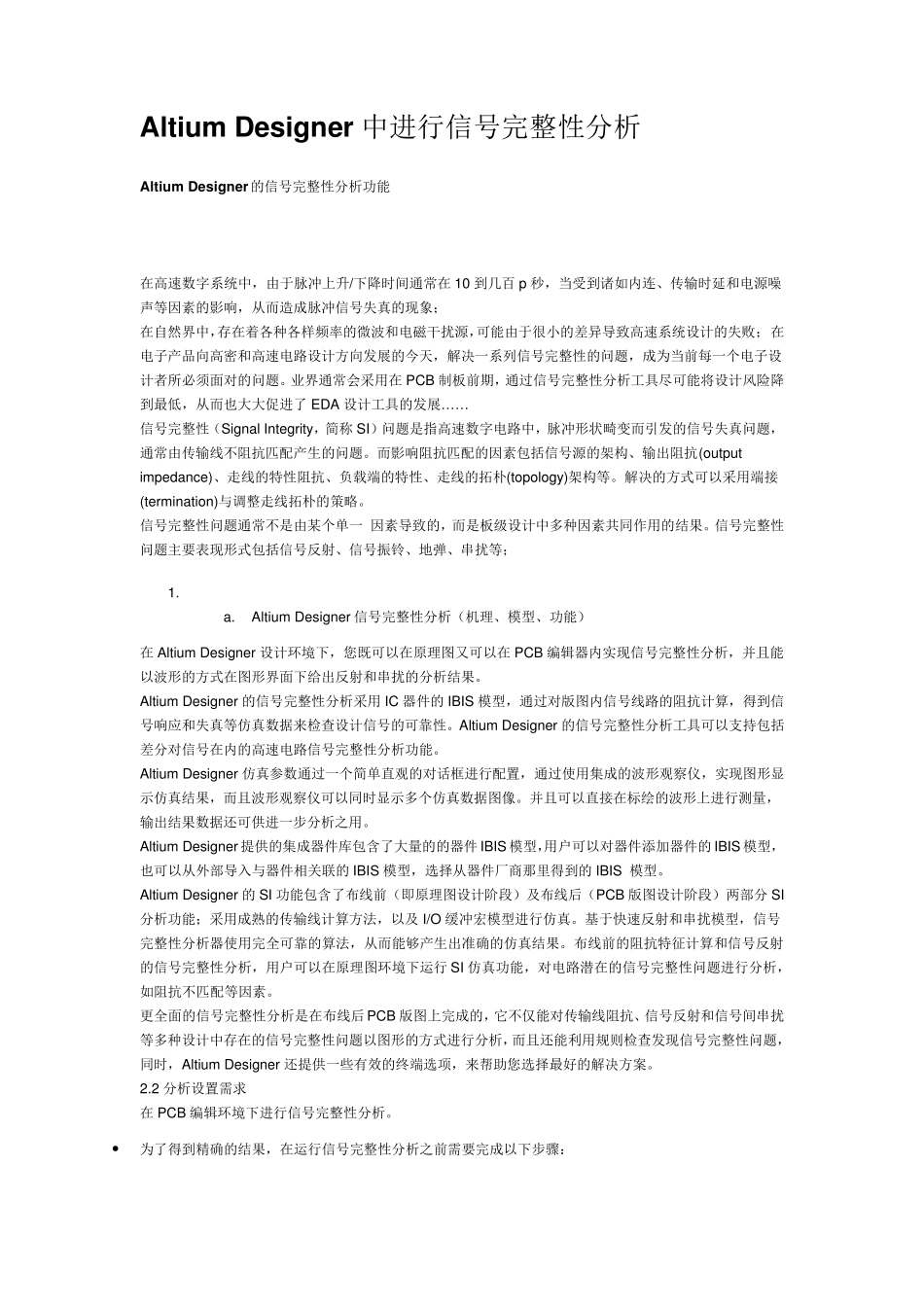

Altium Designer 信号完整性分析(机理、模型、功能) 在Altium Designer 设计环境下,您既可以在原理图又可以在PCB 编辑器内实现信号完整性分析,并且能以波形的方式在图形界面下给出反射和串扰的分析结果

Altium Designer 的信号完整性分析采用 IC 器件的IBIS 模型,通过对版图内信号线路的阻抗计算,得到信号响应和失真等仿真数据来检查设计信号的可靠性

Altium Designer 的信号完整性分析工具可以支持包括差分对信号