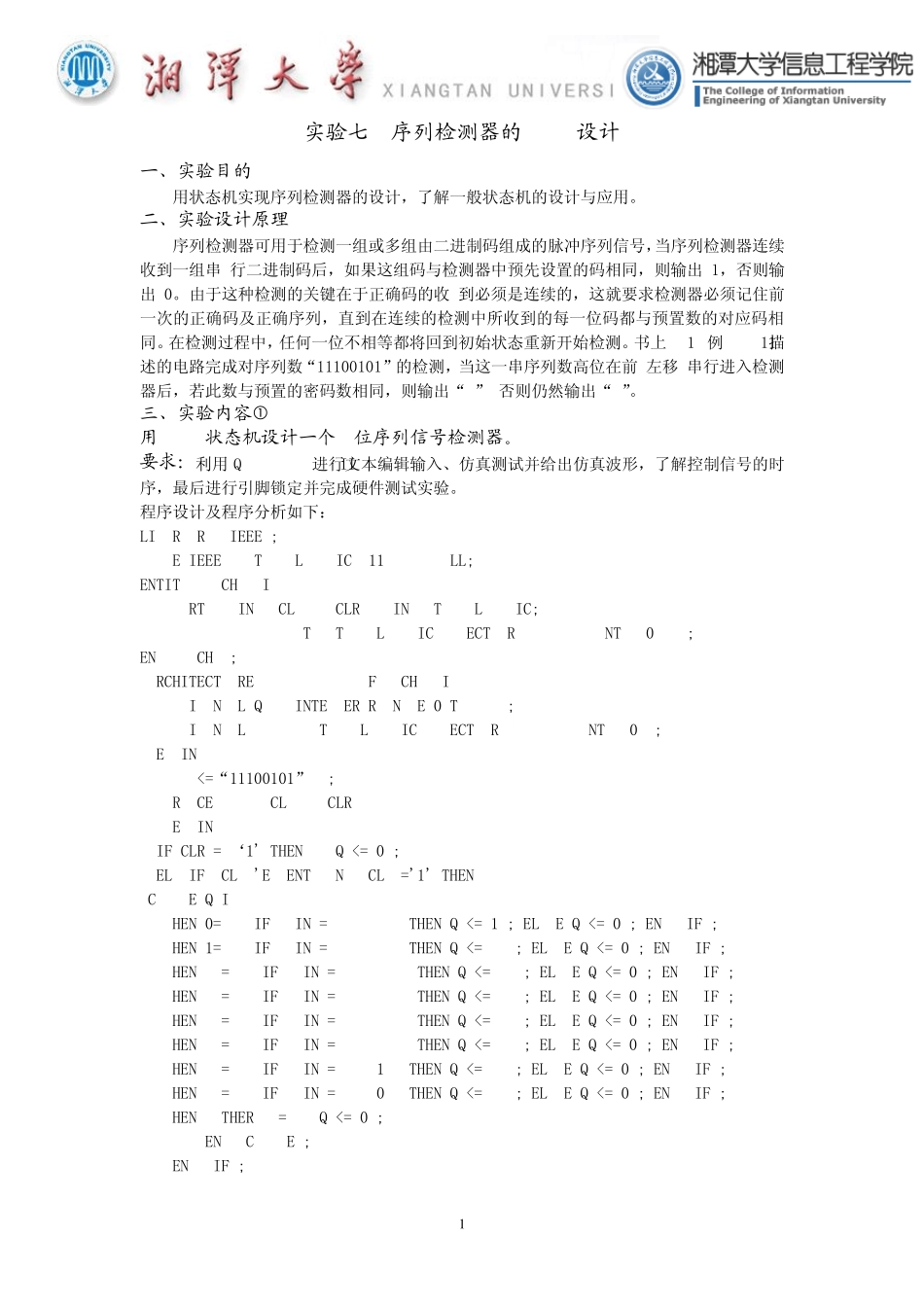

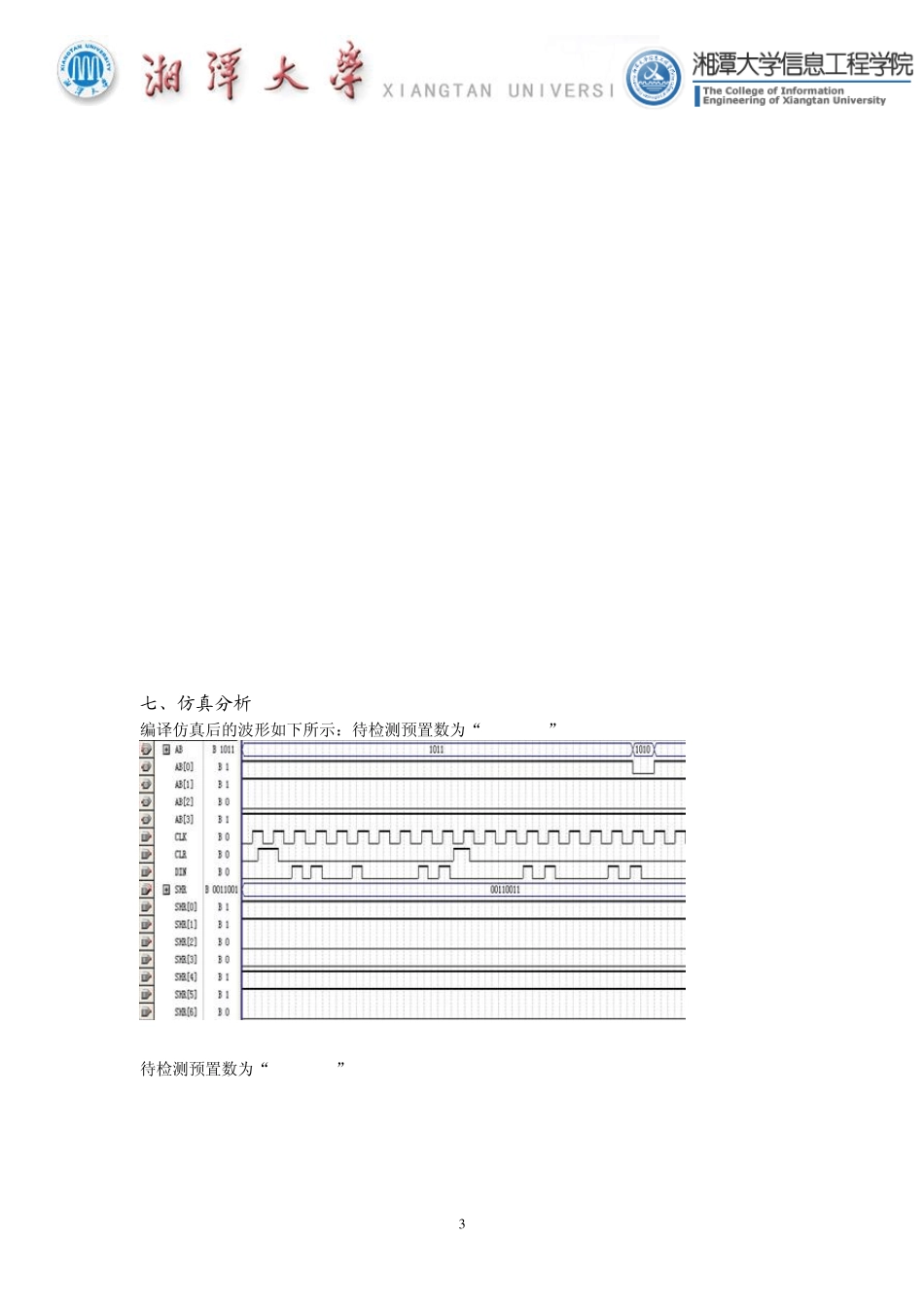

1 实验七 序列检测器的VHDL设计 一、实验目的 用 状 态 机 实 现 序 列 检 测 器 的 设 计 , 了 解 一 般 状 态 机 的 设 计 与 应 用 。 二、实验设计原理 序 列 检 测 器 可 用 于 检 测 一 组 或 多 组 由 二 进 制 码 组 成 的 脉 冲 序 列 信 号 ,当 序 列 检 测 器 连 续收 到 一 组 串 行 二 进 制 码 后 , 如 果 这 组 码 与 检 测 器 中 预 先 设 置 的 码 相 同 , 则 输 出 1, 否 则 输出 0。 由 于 这 种 检 测 的 关 键 在 于 正 确 码 的 收 到 必 须 是 连 续 的 , 这 就 要 求 检 测 器 必 须 记 住 前一 次 的 正 确 码 及 正 确 序 列 , 直 到 在 连 续 的 检 测 中 所 收 到 的 每 一 位 码 都 与 预 置 数 的 对 应 码 相同 。 在 检 测 过 程 中 , 任 何 一 位 不 相 等 都 将 回 到 初 始 状 态 重 新 开 始 检 测 。 书 上 P168例 5-11 描述 的 电 路 完 成 对 序 列 数 “ 11100101” 的 检 测 , 当 这 一 串 序 列 数 高 位 在 前 (左 移 )串 行 进 入 检 测器 后 , 若 此 数 与 预 置 的 密 码 数 相 同 , 则 输 出 “ A” ,否 则 仍 然 输 出 “ B”。 三、实验内容 用 VHDL状态机设计一个 8位序列信号检测器。 要求:利 用QuartusII进 行 文 本 编 辑 输 入 、 仿 真 测 试 并 给 出 仿 真 波 形 , 了 解 控 制 信 号 的 时序 , 最后 进 行 引脚锁定并 完 成 硬件测 试 实 验。 程 序 设 计 及 程 序 分析如 下: LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL; ENTITY SCHK IS PORT(DIN, CLK, CLR : IN STD_LOGIC; AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END SCHK; ARCHITECTURE behav OF SCHK IS SIGNAL Q : INTEGER RANGE 0 TO 8 ; SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN D <= “ 11100101” ; PROCESS( CLK, CLR ) BEGIN IF CLR = ‘1' THEN Q <= 0 ; ELSIF CLK'EVENT AND CLK='1' THEN CASE Q IS WHEN 0=> IF DIN = D(7) THEN Q <= 1 ; EL...