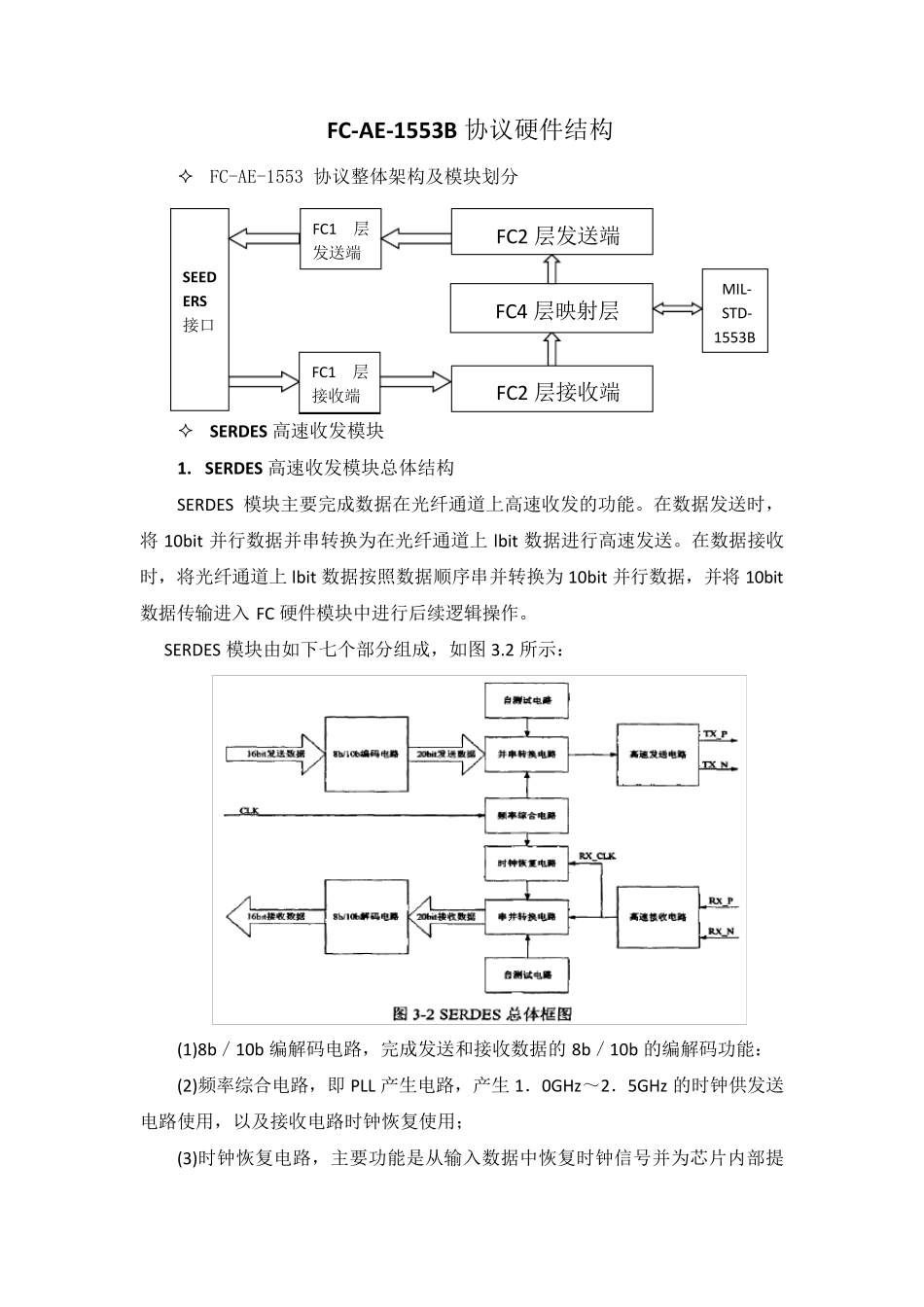

FC-AE-1553B 协议硬件结构 FC-AE-1553 协议整体架构及模块划分 SERDES 高速收发模块 1

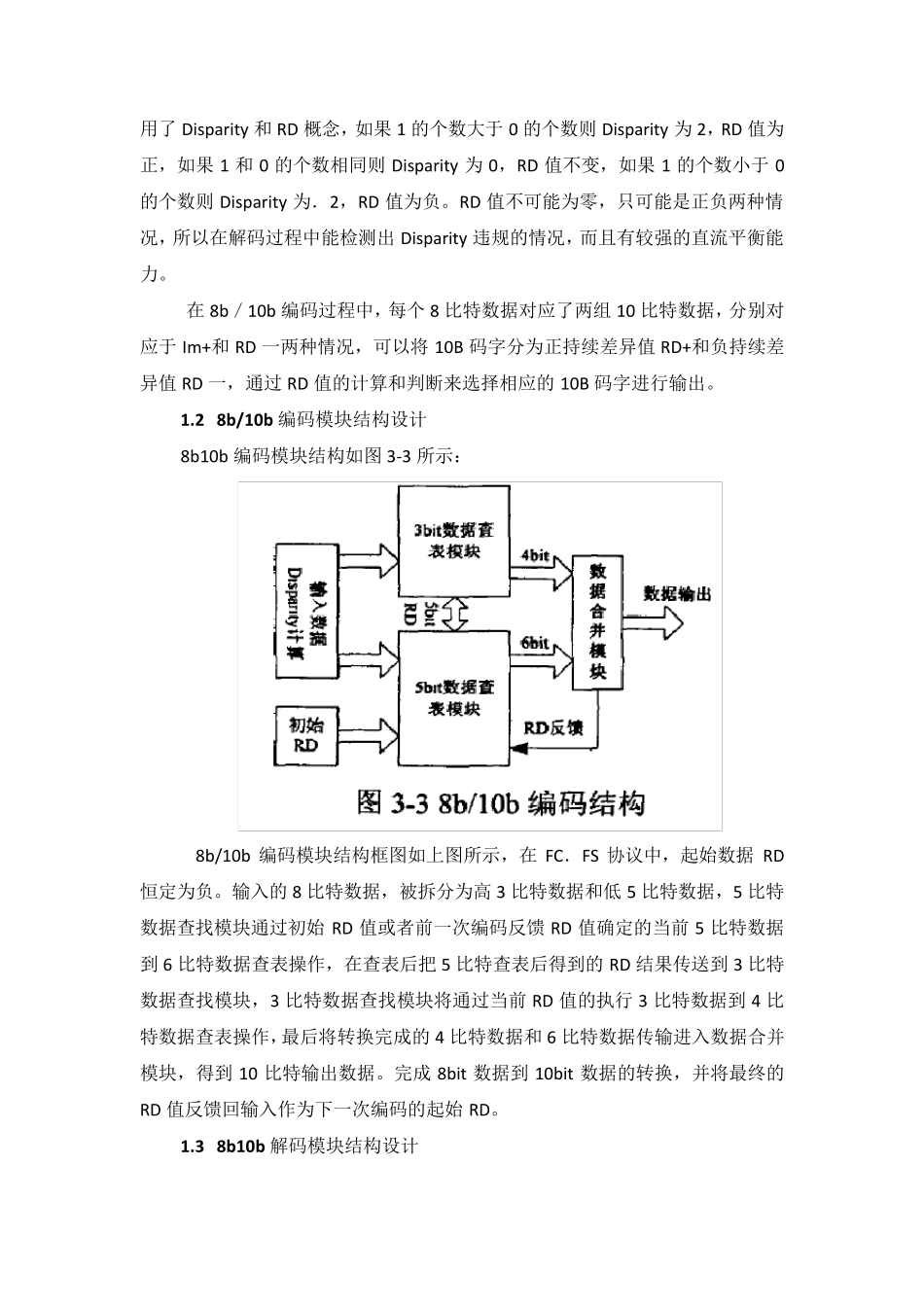

SERDES 高速收发模块总体结构 SERDES 模块主要完成数据在光纤通道上高速收发的功能

在数据发送时,将 10bit 并行数据并串转换为在光纤通道上lbit 数据进行高速发送

在数据接收时,将光纤通道上lbit 数据按照数据顺序串并转换为 10bit 并行数据,并将 10bit数据传输进入 FC 硬件模块中进行后续逻辑操作

SERDES 模块由如下七个部分组成,如图 3

2 所示: (1)8b/10b 编解码电路,完成发送和接收数据的8b/10b 的编解码功能: (2)频率综合电路,即 PLL 产生电路,产生 1.0GHz~2.5GHz 的时钟供发送电路使用,以及接收电路时钟恢复使用; (3)时钟恢复电路,主要功能是从输入数据中恢复时钟信号并为芯片内部提 SEEDERS接口 FC1层接收端 FC1层发送端 FC2 层接收端 FC4 层映射层 MIL- STD- 1553B FC2 层发送端 供工作需要的时钟; (4)高速数据收发电路,采用 LVDS 接口,完成接收发送差分信号的功能; (5)串并转换与并串转换电路,完成发送 10bit 到 lbit 及接收 lbit 到 10bit 的数据串并转换功能; (6)信号质量侦测电路,完成判断差分信号是否符合要求,并给出检测结果: (7)自测试模块电路,完成环路功能检测以及抖动等性能测试,完成 SERDES模块自测试功能; 频率综合电路、时钟恢复电路、高速收发电路、串并与并串电路等涉及到模拟电路设计,而在 XilinxV5 FPGA 中有成熟的 IP RoeketlO 可以直接调用,所以在本系统设计中除了 8b/10b 编解码电路进行详细逻辑设计之外,其余电路结构可以使用口核进行实现

16 位输入