实验一 Qu artu s 使用环境和简单电路设计 一、实验目的 1

熟悉Quartus Ⅱ软件基本使用方法; 2

掌握电路的基本设计方法; 3

掌握电路的基本仿真方法; 4

掌握电路的基本下载方法

二、实验器材 1

KH-310 下载板; 2

KH-310 LED 显示模块

三、文件档名 加载:halfadd

sof 烧录:halfadd

pof 工程项目文件名:halfadd

qpf 四、实验内容 用VHDL 语言和原理图分别完成设计、仿真和下载基本逻辑门电路半加器的过程: 输入:a,b; 输出:求和sum,进位c; 五、实验步骤 1

新建文本文件 在Quartus Ⅱ管理器界面中选择File/New

, 菜单,出现New 对话框,如图3

在对话框中选择VHDL File,点击OK,打开文本编辑器,输入半加器的VHDL 语言程序,如图1

然后保存文件halfadd

需要注意的是,文件名与模块名必须一致

1 Qu artu s Ⅱ 新建文本文件界面 图3

2 输入半加器的VHDL 语言程序 图3

3 保存文件 2

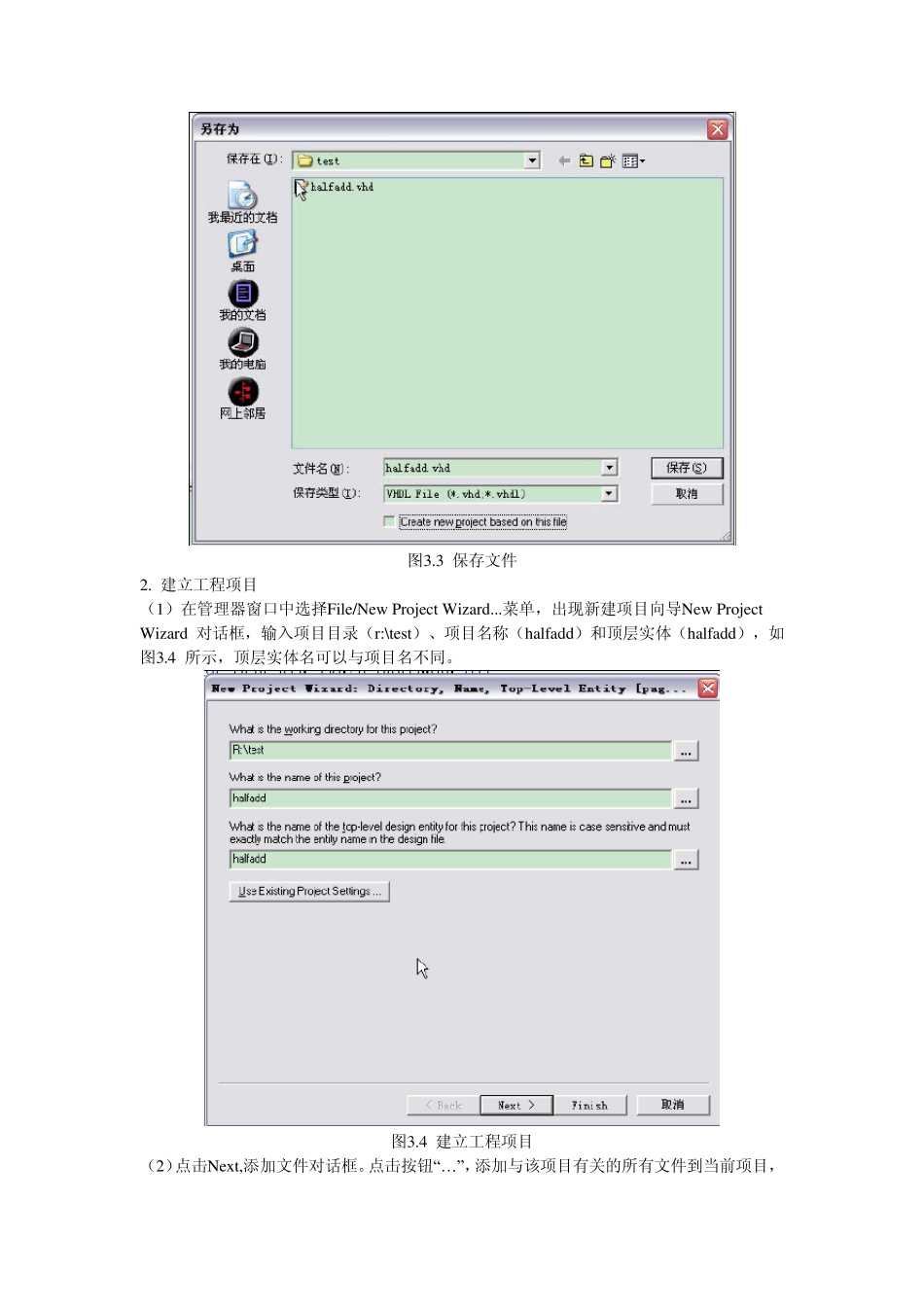

建立工程项目 (1)在管理器窗口中选择File/New Project Wizard

菜单,出现新建项目向导New Project Wizard 对话框,输入项目目录(r:\test)、项目名称(halfadd)和顶层实体(halfadd),如图3

4 所示,顶层实体名可以与项目名不同

4 建立工程项目 (2)点击Next,添加文件对话框

点击按钮“…”,添加与该项目有关的所有文件到当前项目,如图3

本例只有一个文件halfadd

v hd,所以不用添加其它器件

7 添加项目有关的文件 (3)点击Nex t 按钮,再点击Nex t 选择目标器件系列Cy