14 .3 I/O 扩展模块 4.3.1 设计目的及任务 1、设计任务:设计一个基于单片机的 I/O 扩展模块以及相应的外围电路

2、 功能指标:扩展 I/O 数量大于 16 个,可以通过编程控制输入或者输出方向,电源为+5V 供电 3、 设计要求:所设计的 I/O 扩展模块应满足 EDP 实验仪系统设计要求,并能与整个系统有效结合

以下是一个以 8155 I/O 扩展芯片为例的设计范例及其相应电路的讲解,仅供参考

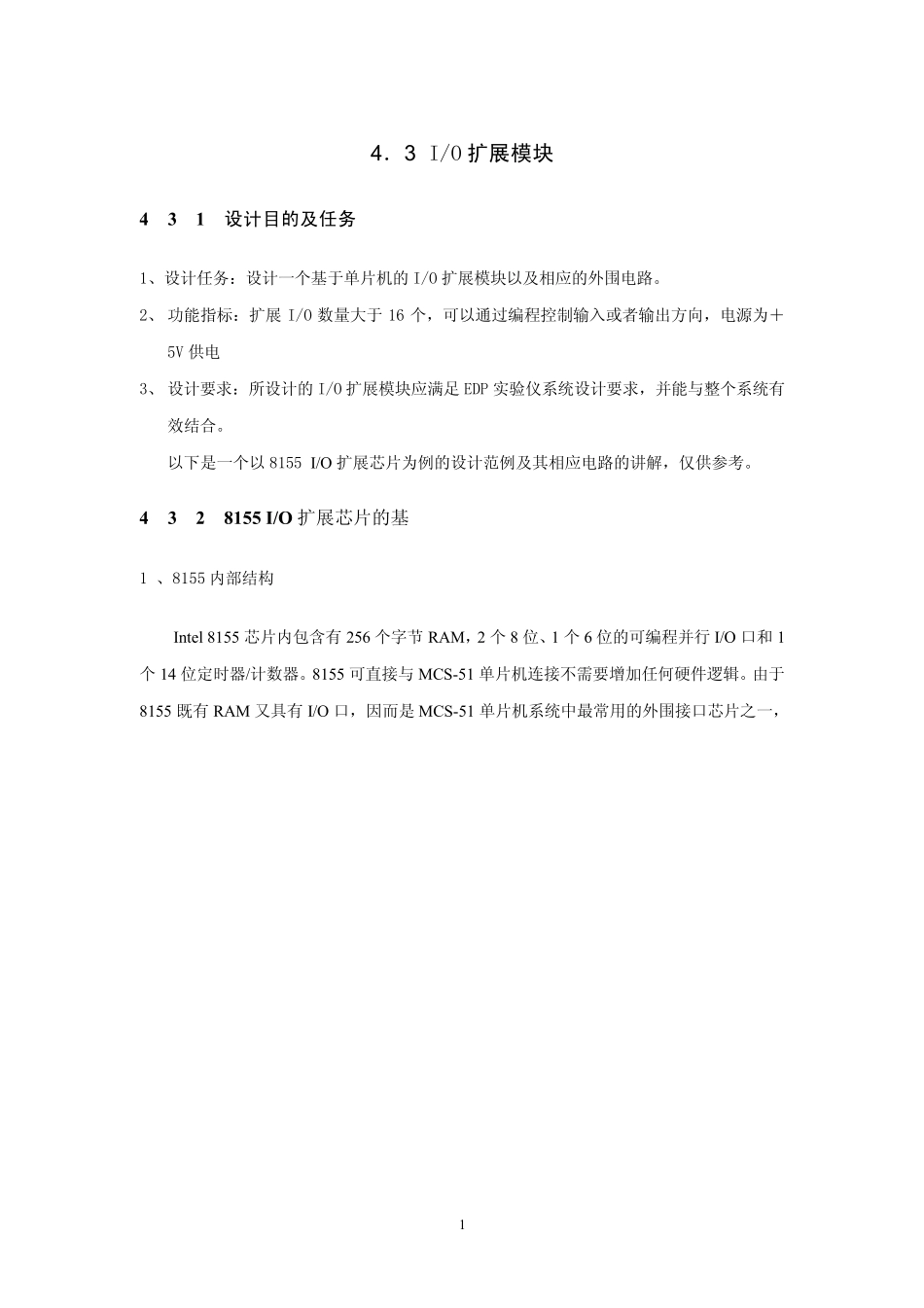

4.3.2 8155 I/O 扩展芯片的基本工作原理 1 、8155 内部结构 Intel 8155 芯片内包含有 256 个字节 RAM,2 个 8 位、1 个 6 位的可编程并行 I/O 口和 1个 14 位定时器/计数器

8155 可直接与 MCS-51 单片机连接不需要增加任何硬件逻辑

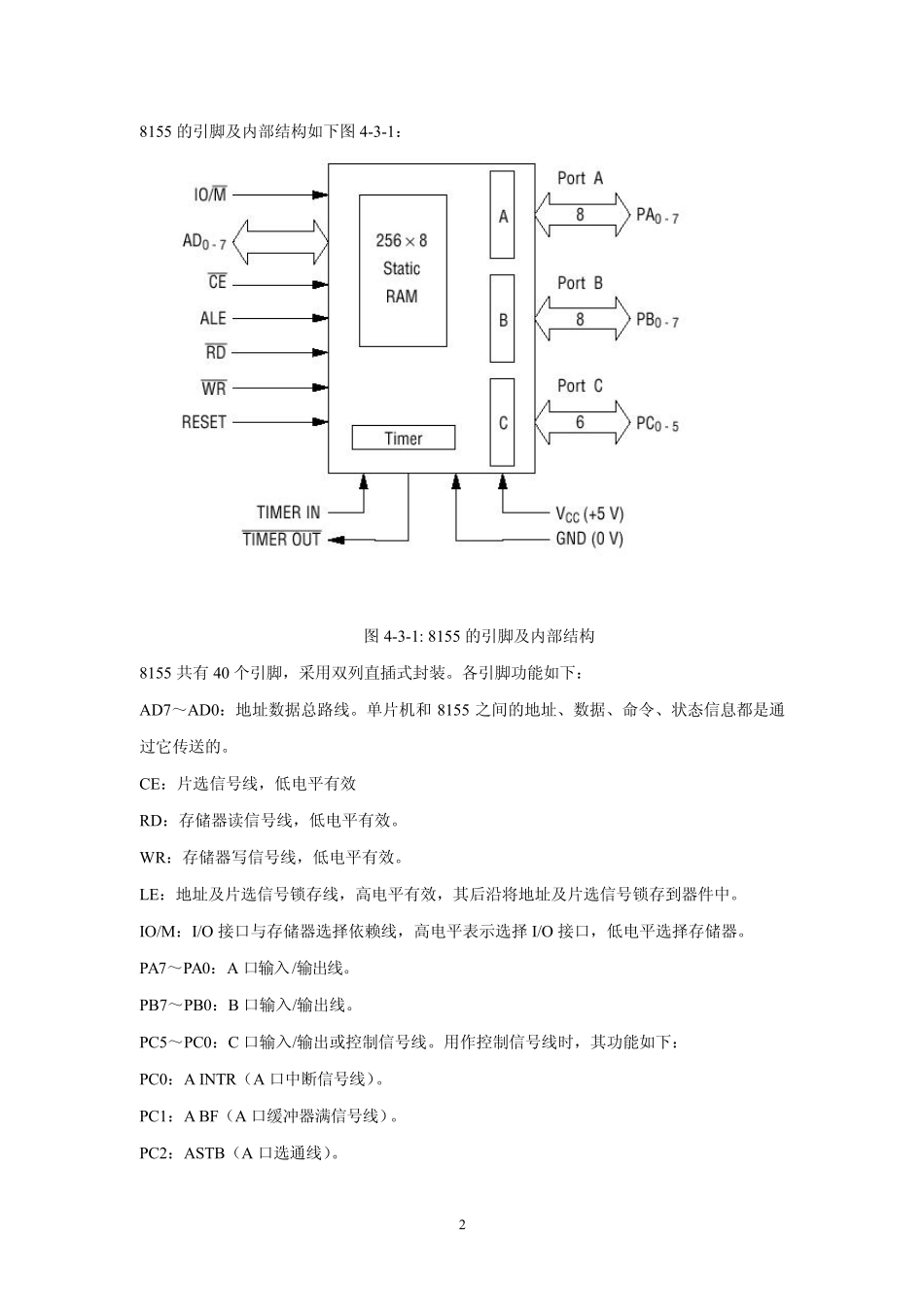

由于8155 既有 RAM 又具有 I/O 口,因而是 MCS-51 单片机系统中最常用的外围接口芯片之一, 28155 的引脚及内部结构如下图4-3-1: 图4-3-1: 8155 的引脚及内部结构 8155 共有40 个引脚,采用双列直插式封装

各引脚功能如下: AD7~AD0:地址数据总路线

单片机和8155 之间的地址、数据、命令、状态信息都是通过它传送的

CE:片选信号线,低电平有效 RD:存储器读信号线,低电平有效

W R:存储器写信号线,低电平有效

LE:地址及片选信号锁存线,高电平有效,其后沿将地址及片选信号锁存到器件中

IO/M:I/O 接口与存储器选择依赖线,高电平表示选择 I/O 接口,低电平选择存储器

PA7~PA0:A 口输入/输出线

PB7~PB0:B 口输入/输出线

PC5~PC0:C 口输入/输出或控制信号线

用作控制信号线时,其功能如下: PC0:A INTR(A 口中断信号线)

PC1:A BF(A 口缓冲器满信号