三人表决器 1、实验目的 掌握在 Qu artu s Ⅱ开发环境下,运用硬件描述语言输入法对“三人表决器”进行设计输入、编译、调试和仿真的方法

“三人表决器”电路的输入为 SW1、SW2 和 SW3,输出为 L3 和 L4,位宽均为 1 位

当 SW1、SW2 和 SW3 中有超过 2 个以上的输入为 1 时, 要求熟悉整个设计流程,从打开、建立文档、编辑、编译、建立激励信号波形及最后仿真的整个过程

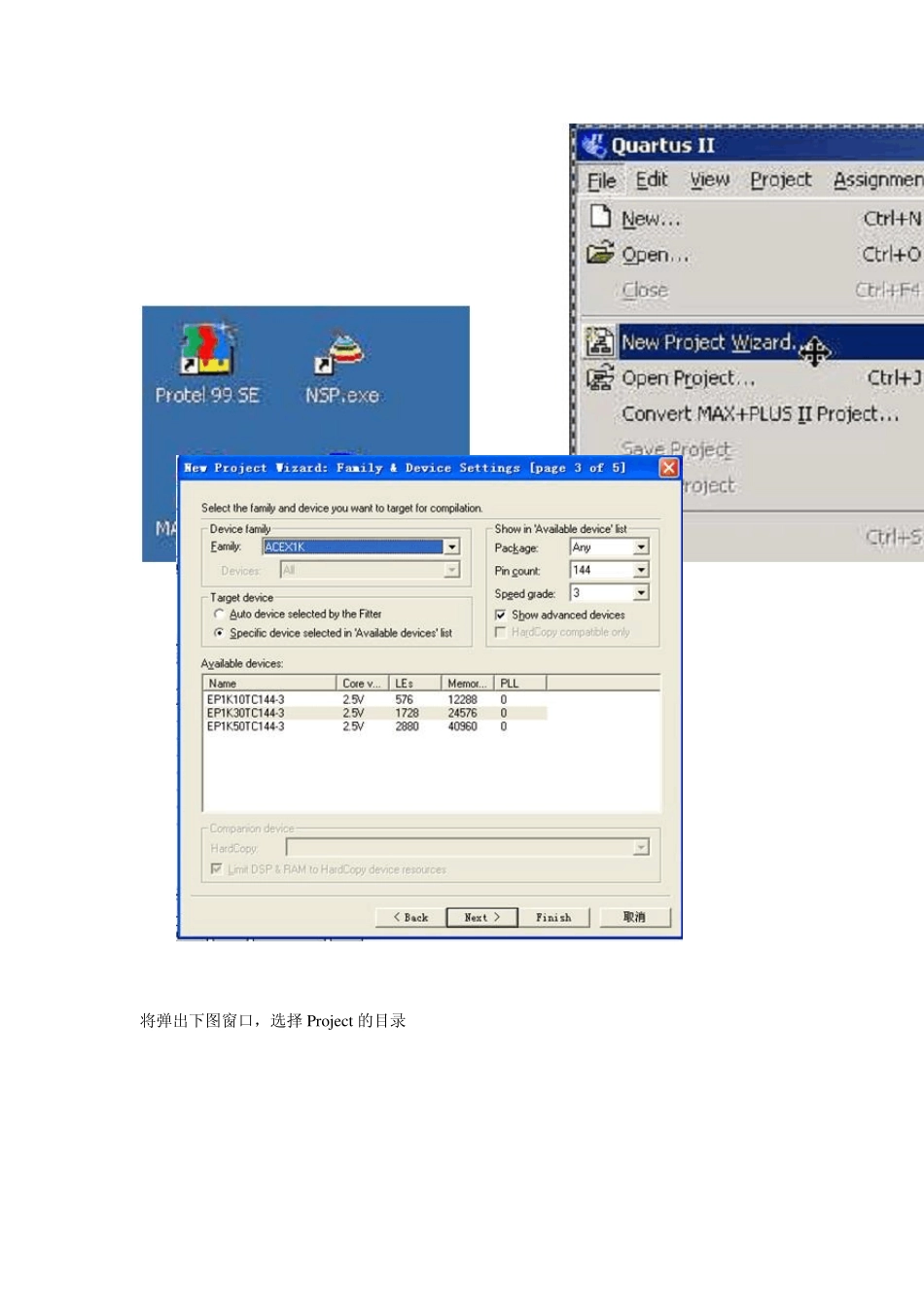

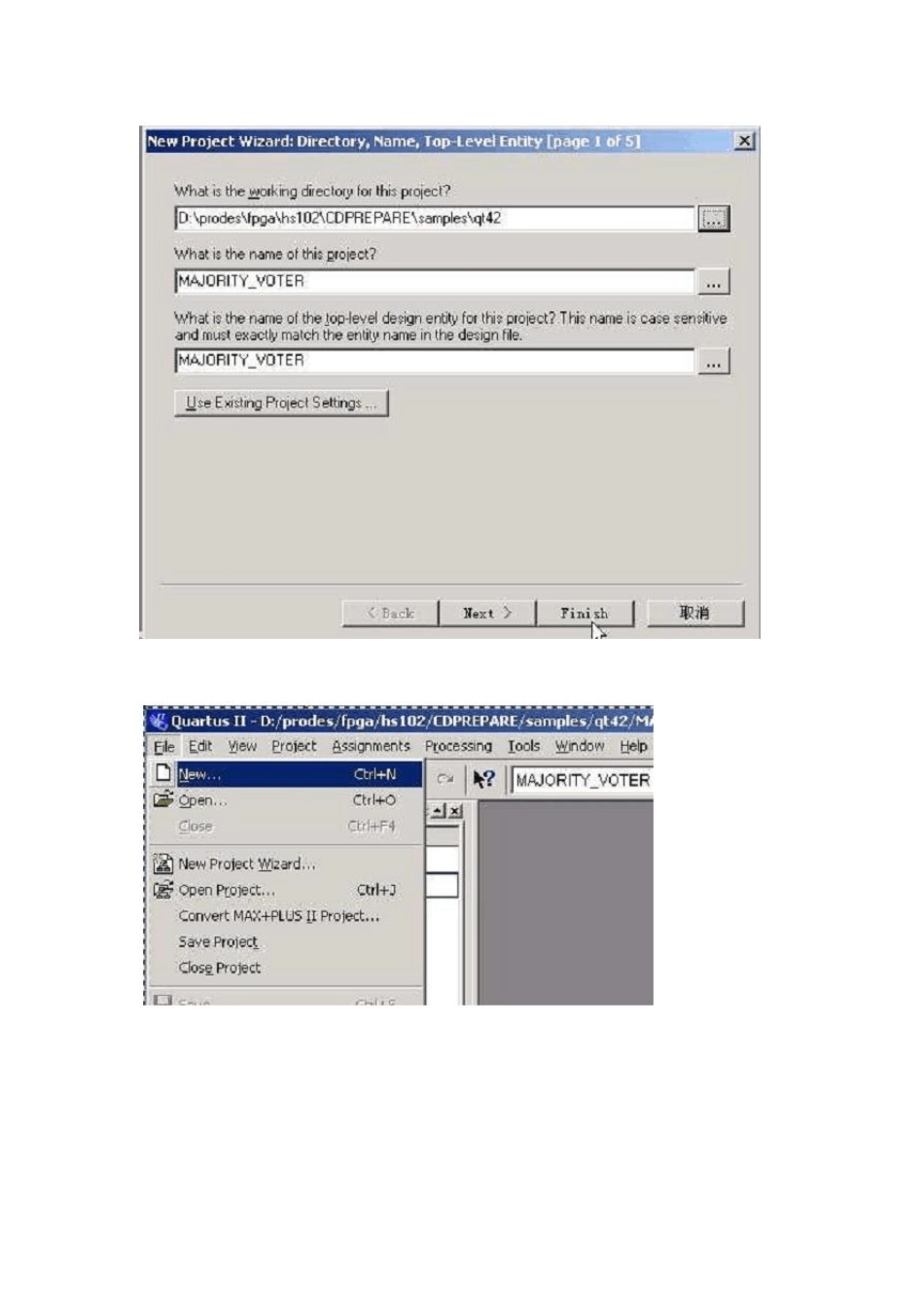

2、实验内容 (1) 在Qu artu s Ⅱ开发环境下,建立工程,并将三人表决器的硬件描述语言程序输入; (2) 完成编译、调试和仿真,分析实验仿真结果,并判断其正确性

3、教学形式 (1) 本实验为验证型实验,学生在实验前预习实验指导书; (2) 指导教师应该在实验前阐述实验目的、内容、方法和步骤,并且就实验中的难点和注意事项进行一定的说明; (3) 实验结束之后,学生按照实验报告的书写格式自行完成实验报告

4、应达到的实验能力标准 (1) 能熟练地在 Qu artu s Ⅱ开发环境下,建立工程,并将三人表决器的硬件描述语言程序输入; (2) 能熟练地进行编译和调试,排除编译后的错误; (3) 正确地在仿真之前进行功能仿真的设置,并熟练地完成功能仿真; (4) 掌握基于 ACEX1K 系列 EP1K30TC144-3器件的时序仿真方法

5 、实验原理 三个人分别用拨位开关 SW1、SW2、SW3 来表示自己的意愿,如果对某决议同意,各人就把自己的拨位开关拨到高电平,不同意就把自己的拨位开关拨到低电平

表决结果用 LED(高电平亮)显示,如果决议通过那么实验板上 L3 灯亮;如果不通过那么实验板上 L3 灯不亮;如果对某个决议有任意二到三人同意,那么此决议通过,L3 亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L3 灯不亮

6、实验步骤 双击 Qu