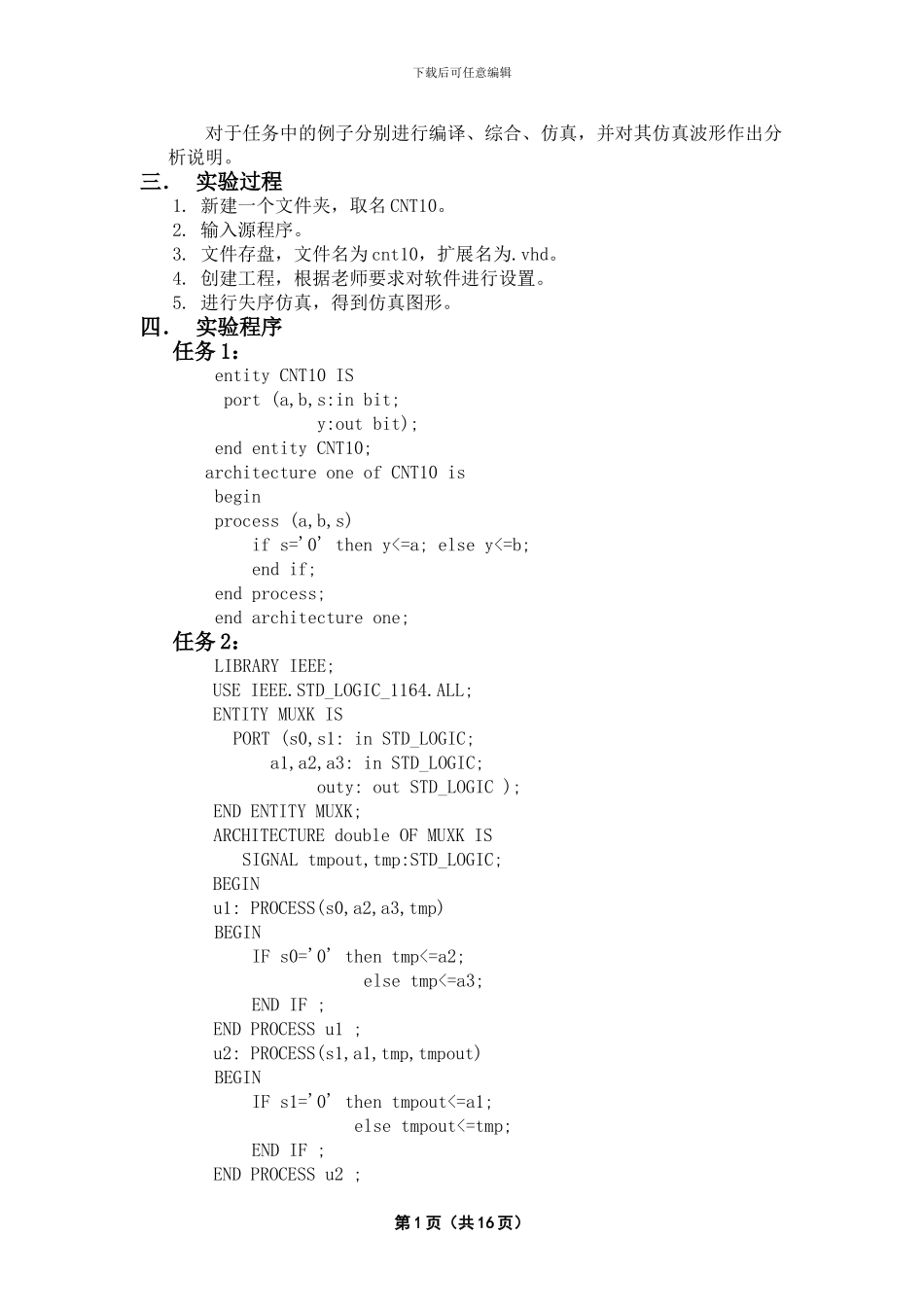

数字系统设计基础实验报告 实验名称: 1. 组合电路设计 ___ 2. 失序电路设计 ___ 3. 计数器的设计 ___ 4. 原理图设计加法器 学 号:___ 08093342__ ____ 姓 名:___ 姚 伟 _______ 班 级: __ 计科 09-1 班 _____ 老 师:__ ______中国矿业大学计算机学院2011 年 10 月 27 日实验一:组合电路的设计一. 实验目的熟悉 QuartusⅡ 的 VHDL 文本设计流程全过程,学习简单组合电路的设计、仿真和硬件测试。二. 实验任务任务 1:利用 QuartusⅡ 完成 2 选 1 多路选择器的文本编辑输入和仿真测试等步骤,得出仿真波形。最后在试验系统上进行硬件测试,验证本项设计的功能。任务 2:将此多路选择器看成是一个元件 mux21a,利用元件例化语句描述电路图,并将此文件放在同一目录中。下载后可任意编辑对于任务中的例子分别进行编译、综合、仿真,并对其仿真波形作出分析说明。三. 实验过程1. 新建一个文件夹,取名 CNT10。2. 输入源程序。3. 文件存盘,文件名为 cnt10,扩展名为.vhd。4. 创建工程,根据老师要求对软件进行设置。5. 进行失序仿真,得到仿真图形。四. 实验程序任务 1:entity CNT10 IS port (a,b,s:in bit; y:out bit);end entity CNT10;architecture one of CNT10 is beginprocess (a,b,s) if s='0' then y<=a; else y<=b; end if;end process;end architecture one;任务 2: LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUXK IS PORT (s0,s1: in STD_LOGIC; a1,a2,a3: in STD_LOGIC; outy: out STD_LOGIC );END ENTITY MUXK;ARCHITECTURE double OF MUXK IS SIGNAL tmpout,tmp:STD_LOGIC;BEGINu1: PROCESS(s0,a2,a3,tmp) BEGIN IF s0='0' then tmp<=a2; else tmp<=a3; END IF ;END PROCESS u1 ;u2: PROCESS(s1,a1,tmp,tmpout) BEGIN IF s1='0' then tmpout<=a1; else tmpout<=tmp; END IF ; END PROCESS u2 ; 第 1 页(共 16 页)下载后可任意编辑outy<=tmpout;END ARCHITECTURE double;五. 实验结果 任务 1: 任务 2: 第 2 页(共 16 页)下载后可任意编辑六. 实验体会在课堂上对于“EDA 与 VHDL”这门课的用处及用法一直一知半解,课上对于一些编程也是学的很模糊,因为学习过模拟电路与数字电路,所以总认为器件仿真要用电脑模拟器件或者直接用实物,但...