精品文档---下载后可任意编辑软件实验教程2024 年 4 月目录实验一自上而下(Top-Down)的电路设计 3Lab 1

1 启动软件 1 Lab 1

2 自上而下的系统级仿真 1 Lab 1

3 电路图输入 3 Lab 1

4 模块的创建 5 Lab 1

5 电源的创建 6 Lab 1

6 建立运放测试电路 7 实验二使用 S pectre Direct 进行模拟仿真 7 Lab 2

1 运行仿真 7 Lab 2

2 使用激励模板 13 Lab 2

3 波形窗的使用 15 Lab 2

4 保存仿真状态 18 Lab 2

5 将仿真结果注释在电路图窗口 18 实验一 自上而下(Top-Down)的电路设计Lab 1

1 启动软件实验目的:掌握如何启动模拟电路设计环境

实验步骤:1

进入 Linux 界面后,点击鼠标右键,选中 New Terminal,则会弹出一个交互终端

进入教程所在目录后,输入命令 cdArtist446 (注意:cd 后必须有空格;命令行大小写敏感)3

在同一个交互终端内,输入命令 icms &,在屏幕底部会出现一个命令交互窗(Command Interpreter Window,CIW)

假如出现 What’s New 窗口,可使用 File-Close 命令关闭

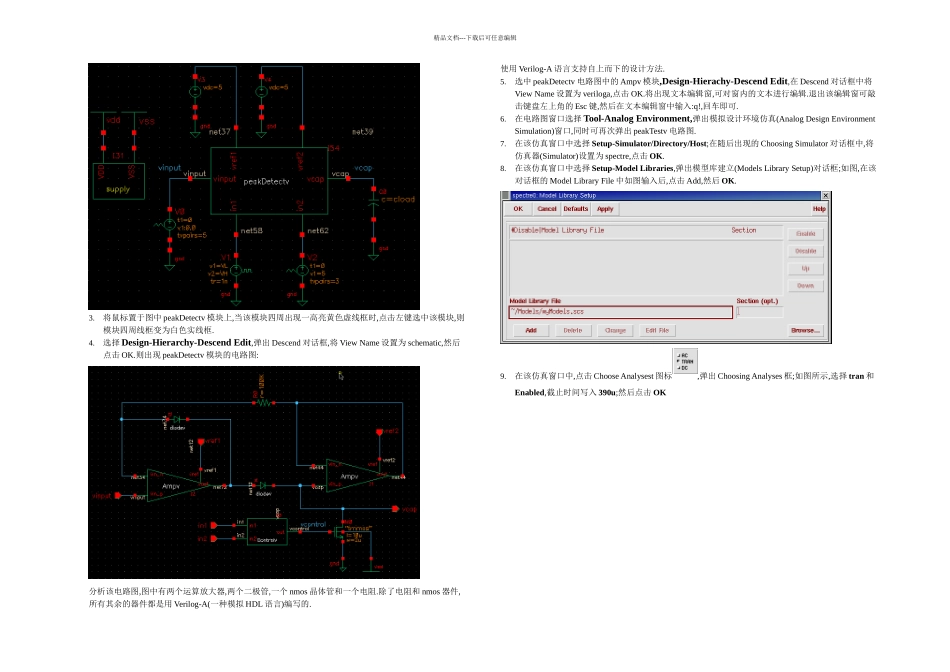

2 自上而下的系统级仿真实验目的:掌握如何对含 AHDL 模块的模块级设计进行仿真

实验步骤:1

在 CIW 中选择 Tool-Library Manager,会弹出库管理器(Library Manager)

在库管理器中,用鼠标左键选中 training,则 cell 中会显示出 training 库中所有的 cell;在 training 的所有cell 中用左键选中 peakTestv;用鼠标中键(或右键)打开(open)view 中的 schematic