实验五:数字锁相环与位同步 一、 实验目的 1

掌握数字锁相环工作原理以及触发式数字锁相环的快速捕获原理

掌握用数字环提取位同步信号的原理及对信息代码的要求

掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念

二、 实验内容 1

观察数字环的失锁状态、锁定状态

观察数字环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差、信息代码的关系

观察数字环位同步器的同步保持时间与固有频差之间的关系

三、 基本原理 可用窄带带通滤波器,锁相环来提取位同步信号

实验一中用模数混合锁相环(电荷泵锁相环)提取位同步信号,它要求输入信号是一个准周期数字信号

实验三中的模拟环也可以提取位同步信号,它要求输入准周期正弦信号

本实验使用数字锁相环提取位同步信号,它不要求输入信号一定是周期信号或准周期信号,其工作频率低于模数环和模拟环

用于提取位同步信号的数字环有超前滞后型数字环和触发器型数字环,此实验系统中的位同步提取模块用的是触发器型数字环,它具有捕捉时间短、抗噪能力强等特点

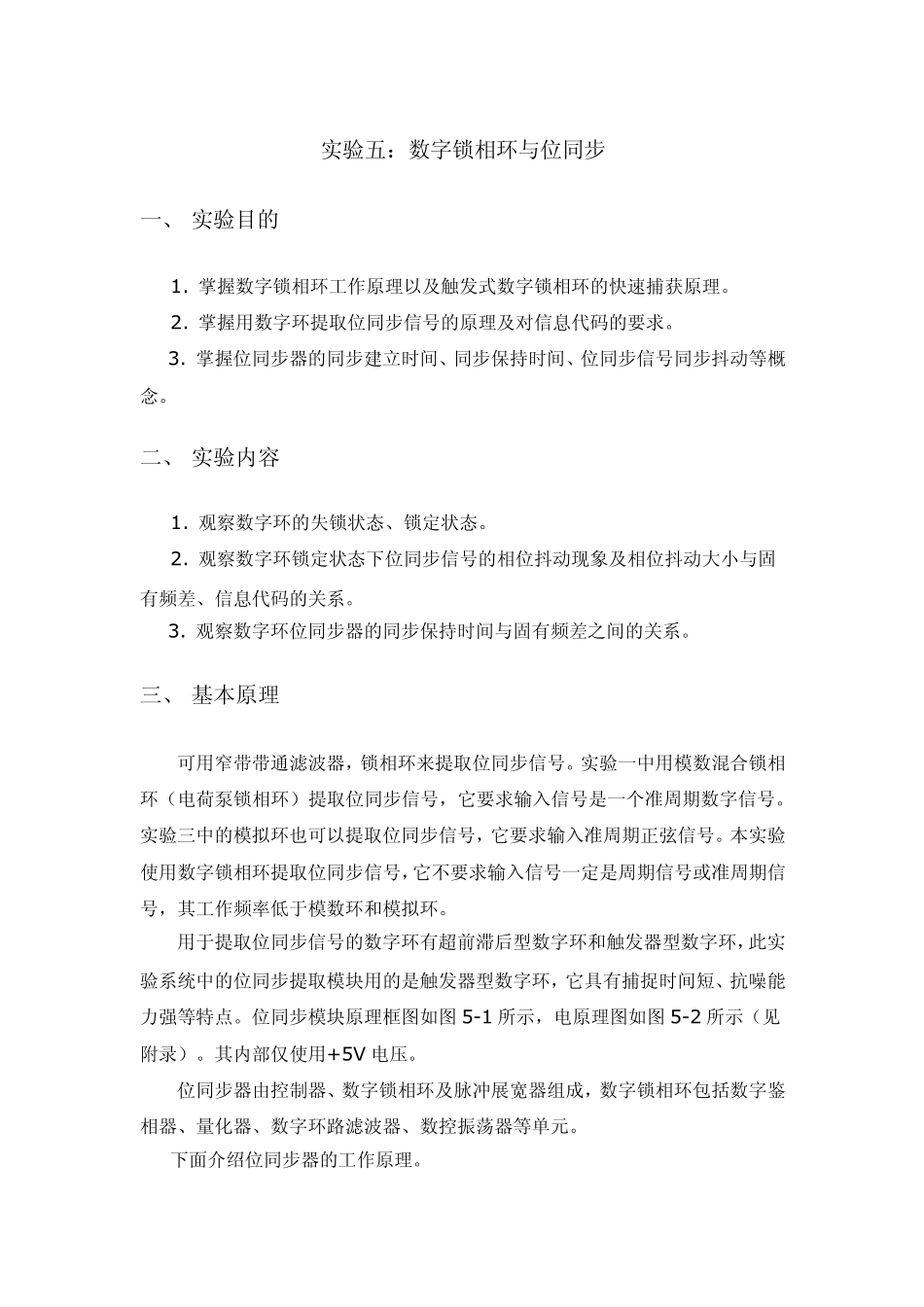

位同步模块原理框图如图 5-1 所示,电原理图如图 5-2 所示(见附录)

其内部仅使用+5V 电压

位同步器由控制器、数字锁相环及脉冲展宽器组成,数字锁相环包括数字鉴相器、量化器、数字环路滤波器、数控振荡器等单元

下面介绍位同步器的工作原理

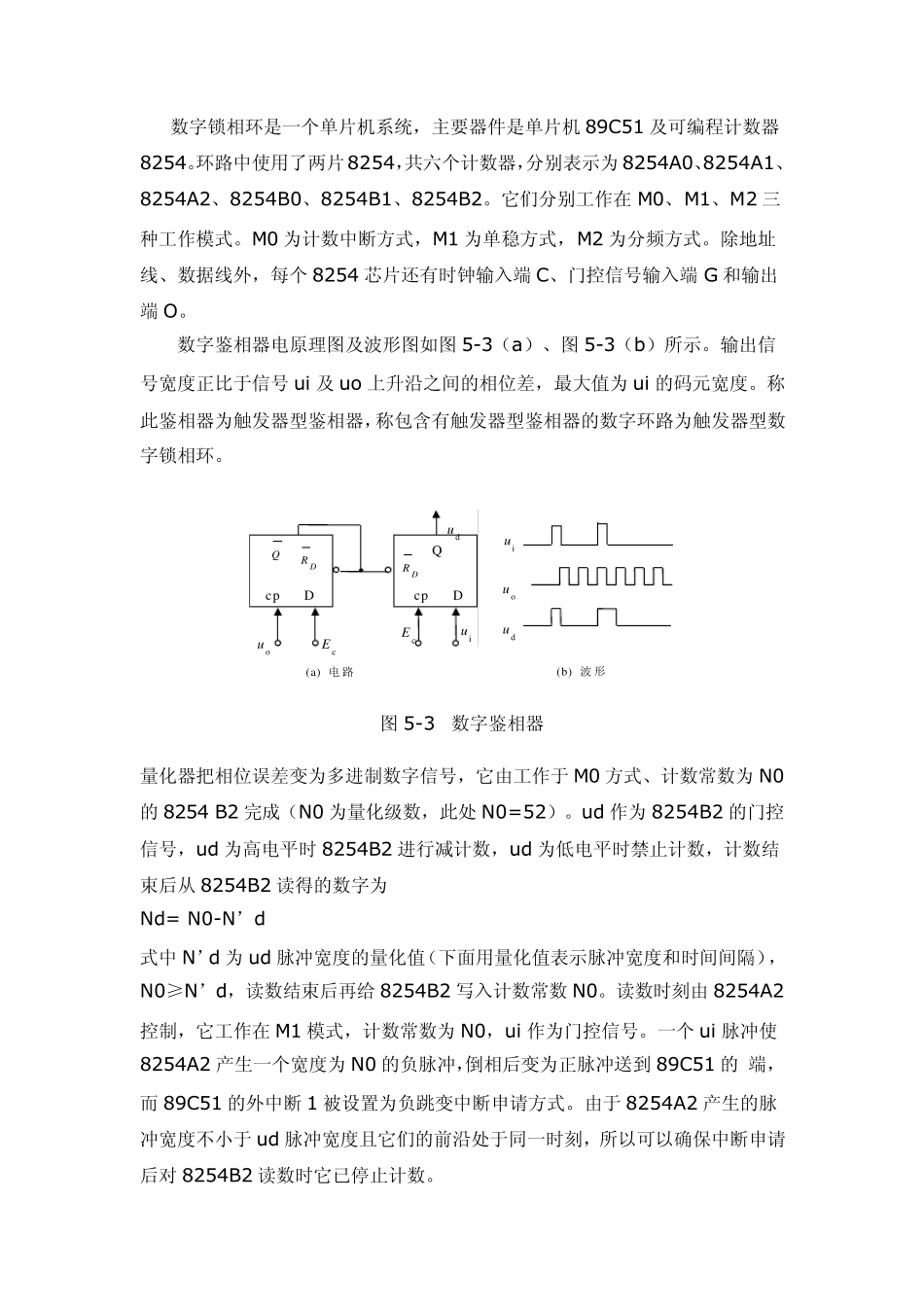

数字锁相环是一个单片机系统,主要器件是单片机 89C51 及可编程计数器8254

环路中使用了两片8254,共六个计数器,分别表示为 8254A0、8254A1、8254A2、8254B0、8254B1、8254B2

它们分别工作在 M0、M1、M2 三种工作模式

M0 为计数中断方式,M1 为单稳方式,M2 为分频方式

除地址线、数据线外,每个 8254 芯片还有时钟输入端 C、门控信号输入端 G 和输出端 O