A20 User Manual (Revision 1

0) Copyright © 2013 Allwinner Technology Co

All Rights Reserved

Page 240 / 835 1

Port Controller 1

Port Description The chip has several ports for multi-functional input/out pins

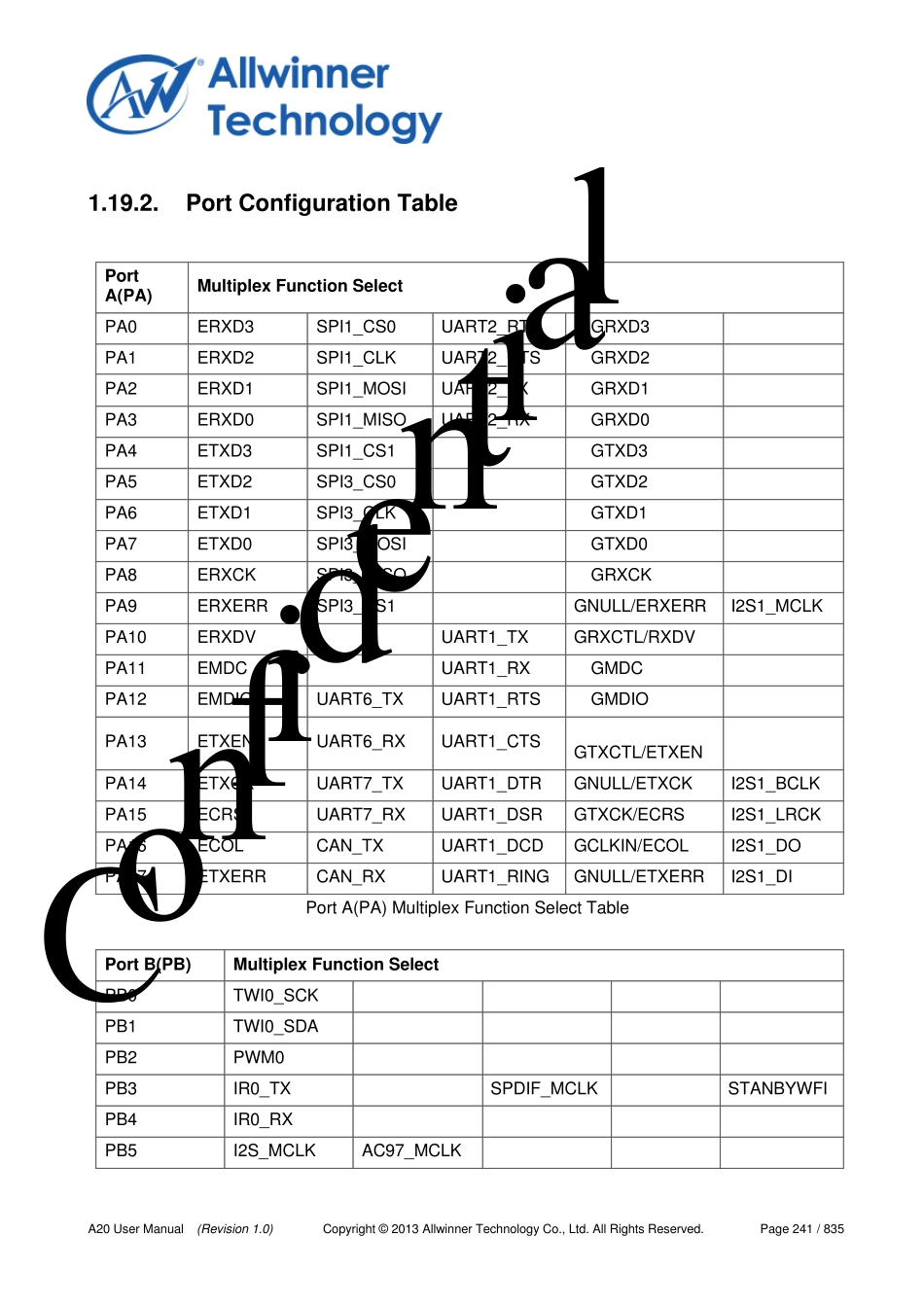

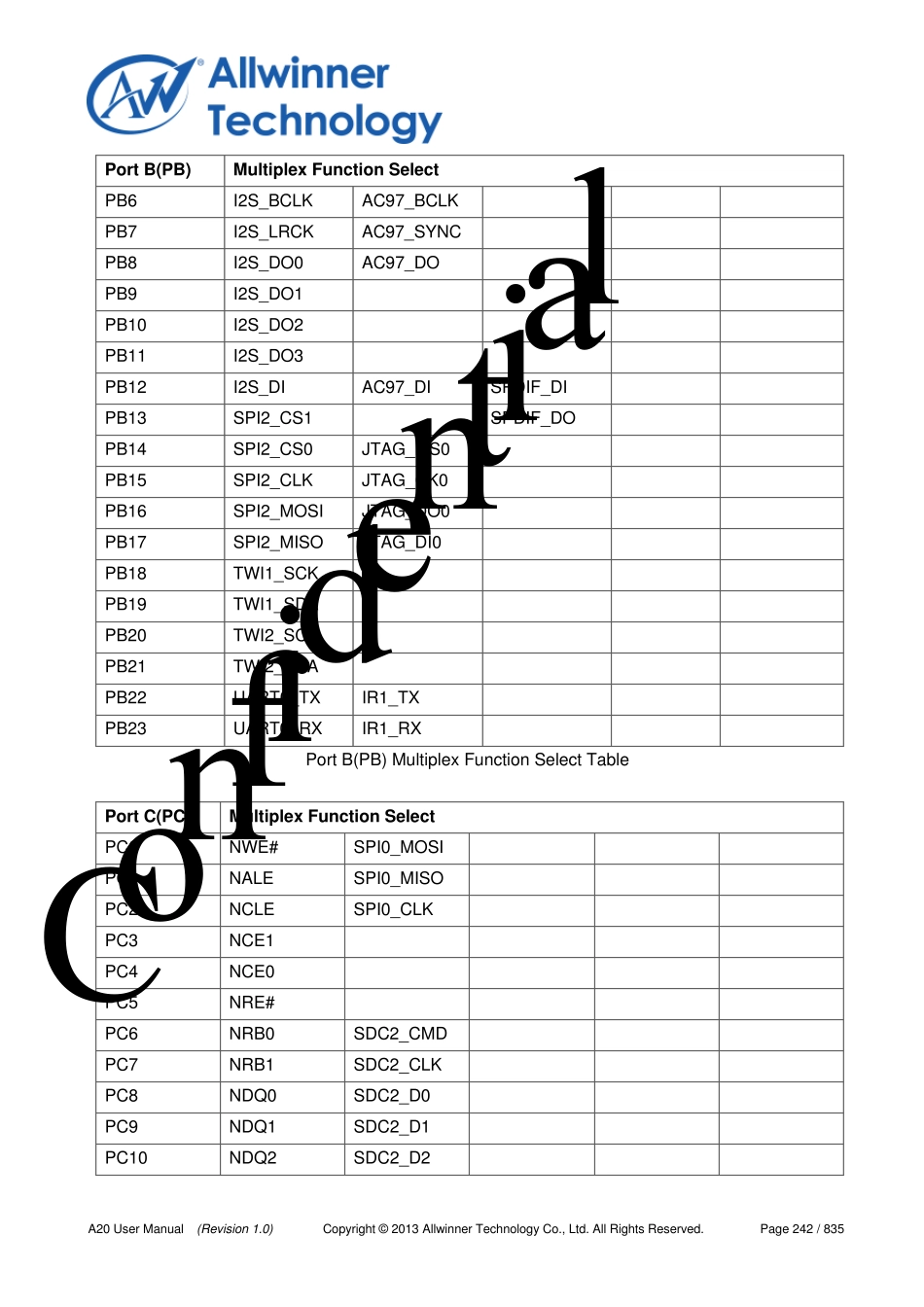

They are shown below: Port A(PA): 18 input/output port Port B(PB): 24 input/output port Port C(PC): 25 input/output port Port D(PD): 28 input/output port Port E(PE) : 12 input/output port Port F(PF) : 6 input/output port Port G(PG) : 12 input/output port Port H(PH) : 28 input/output port Port I(PI) : 22 input/output port Port S(PS) : 84 input/output port for DRAM controller For various system configurations, these ports can be easily configured by software

All these ports (except PS) can be configured as GPIO if multiplexed functions not used

32 external PIO interru