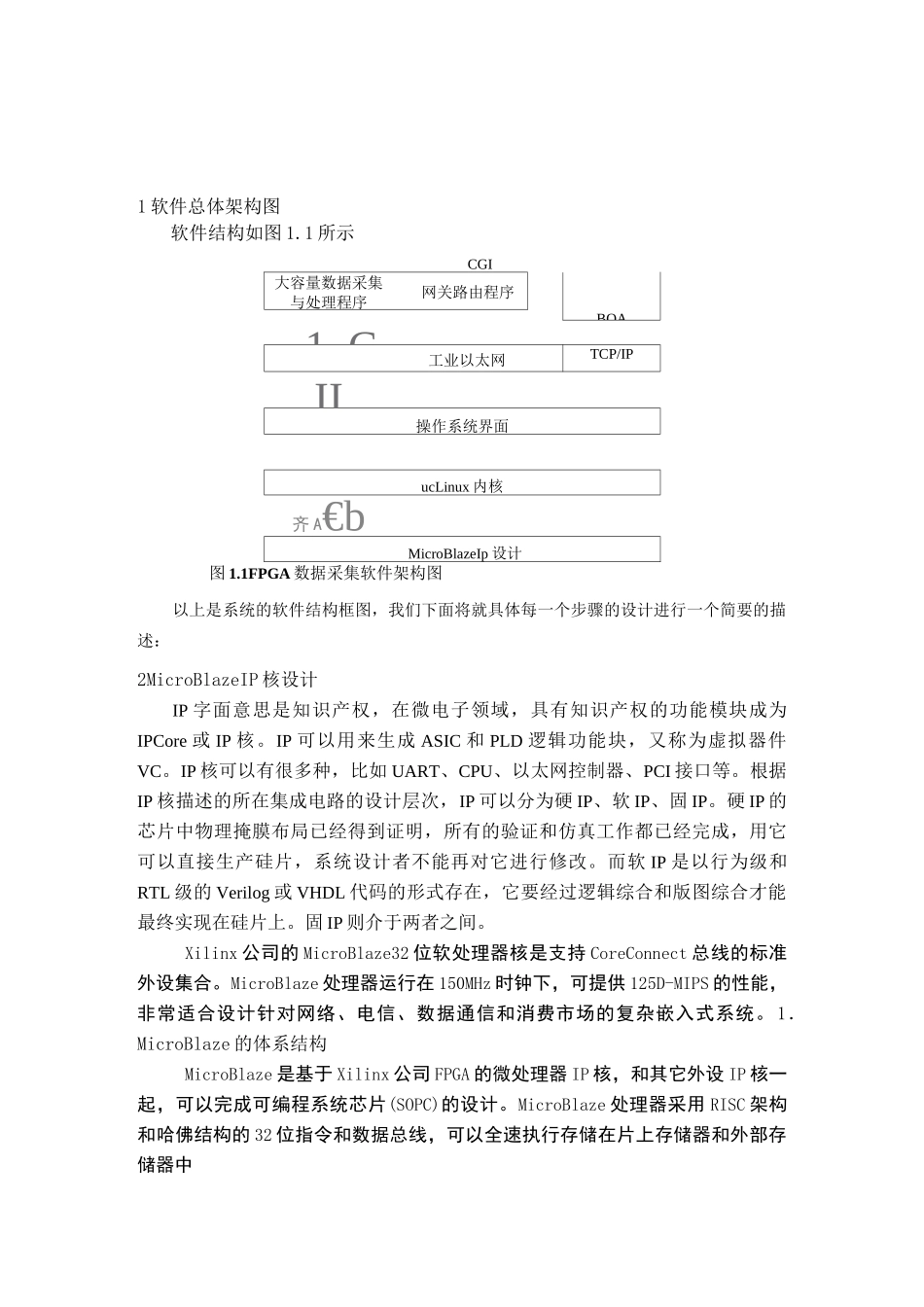

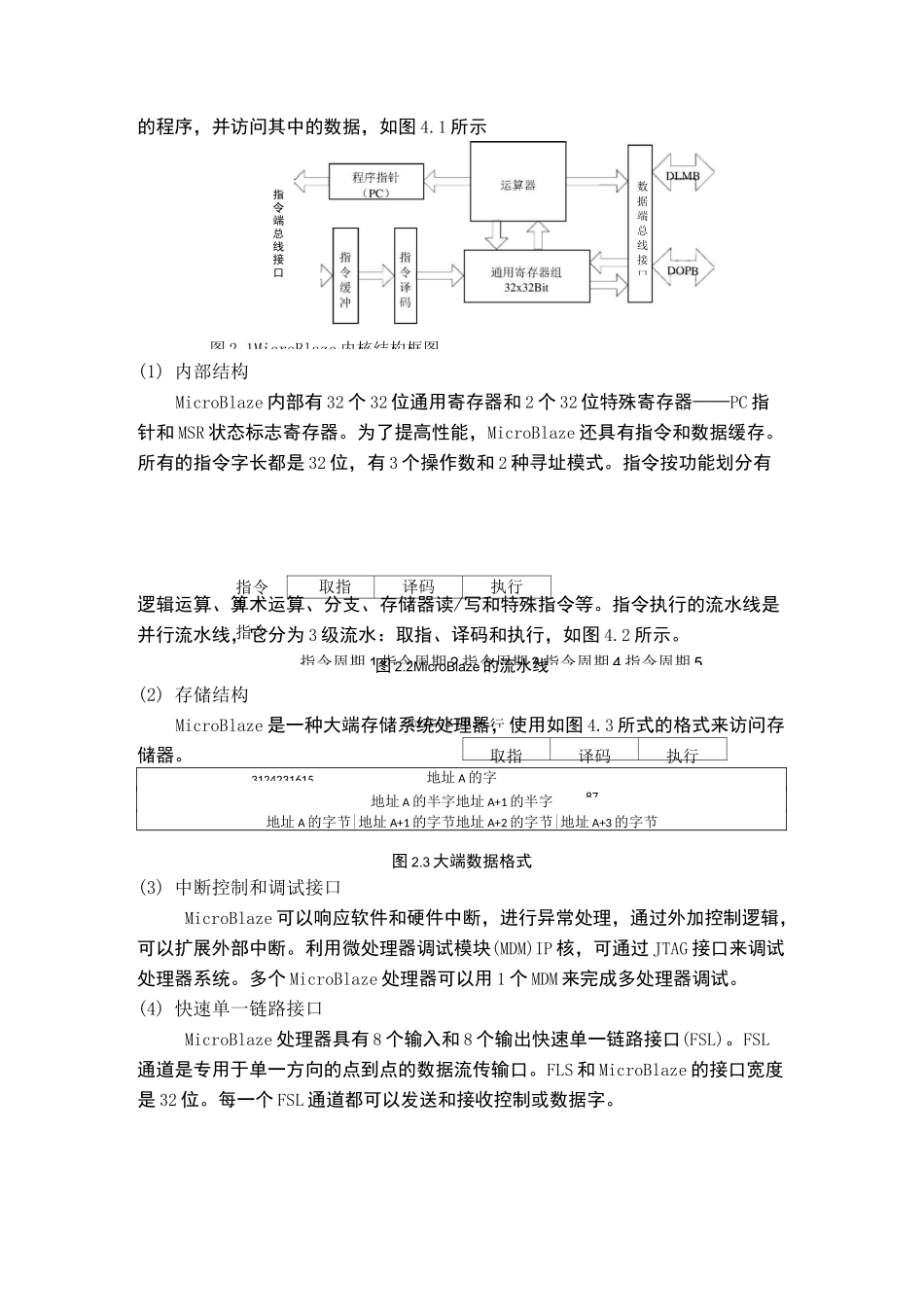

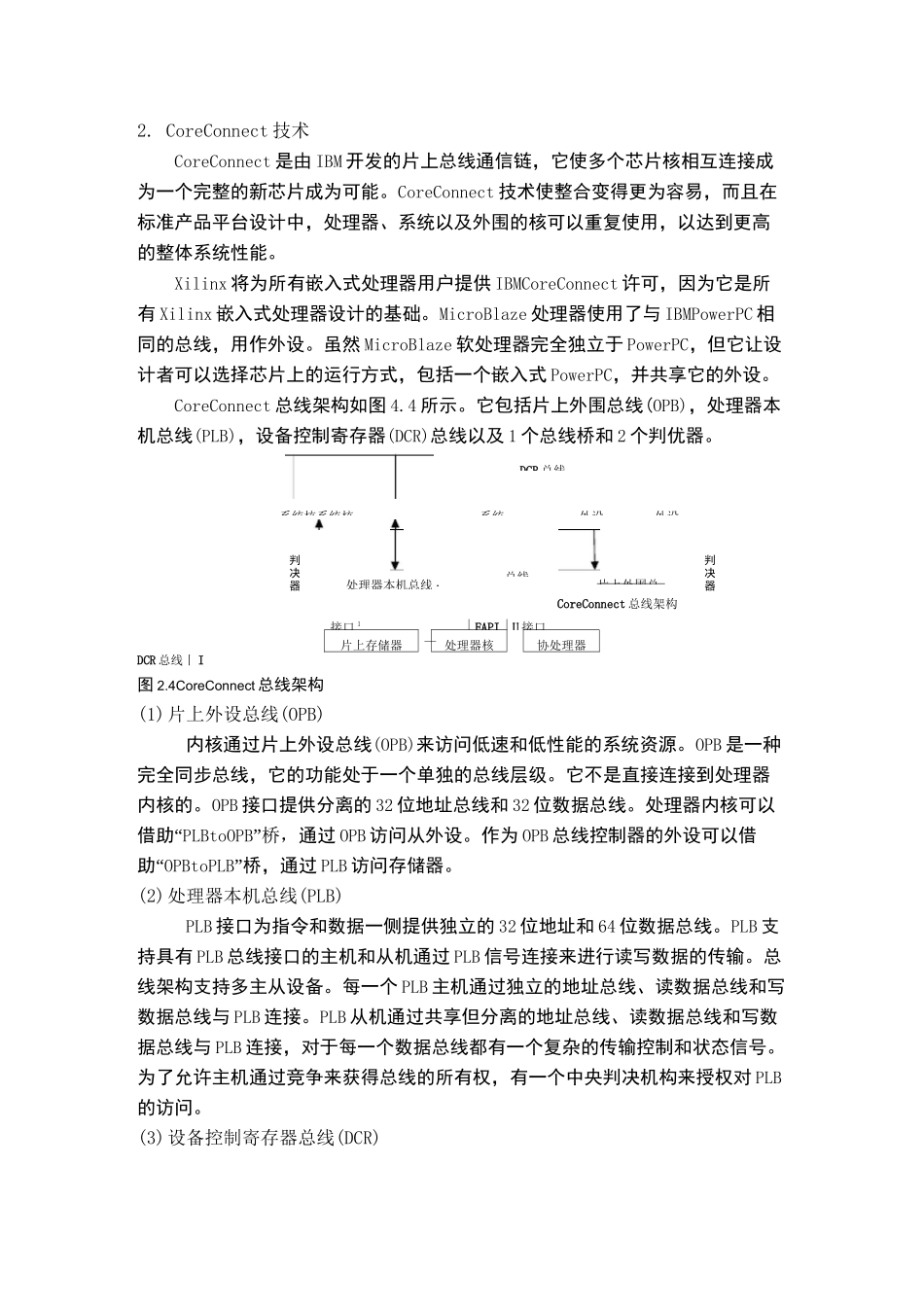

1 软件总体架构图软件结构如图 1.1 所示CGI大容量数据采集与处理程序网关路由程序BOA1..C工业以太网TCP/IPII操作系统界面ucLinux 内核齐 A€bMicroBlazeIp 设计图 1.1FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2MicroBlazeIP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IPCore 或 IP 核。IP 可以用来生成 ASIC 和 PLD 逻辑功能块,又称为虚拟器件VC。IP 核可以有很多种,比如 UART、CPU、以太网控制器、PCI 接口等。根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬 IP、软 IP、固 IP。硬 IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。而软 IP 是以行为级和RTL 级的 Verilog 或 VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。固 IP 则介于两者之间。Xilinx 公司的 MicroBlaze32 位软处理器核是支持 CoreConnect 总线的标准外设集合。MicroBlaze 处理器运行在 150MHz 时钟下,可提供 125D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。1.MicroBlaze 的体系结构MicroBlaze 是基于 Xilinx 公司 FPGA 的微处理器 IP 核,和其它外设 IP 核一起,可以完成可编程系统芯片(SOPC)的设计。MicroBlaze 处理器采用 RISC 架构和哈佛结构的 32 位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中指令1指令2取指译码执行取指译码执行312423161587的程序,并访问其中的数据,如图 4.1 所示(1) 内部结构MicroBlaze 内部有 32 个 32 位通用寄存器和 2 个 32 位特殊寄存器——PC 指针和 MSR 状态标志寄存器。为了提高性能,MicroBlaze 还具有指令和数据缓存。所有的指令字长都是 32 位,有 3 个操作数和 2 种寻址模式。指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。指令执行的流水线是并行流水线,它分为 3 级流水:取指、译码和执行,如图 4.2 所示。图 2.2MicroBlaze 的流水线(2) 存储结构MicroBlaze 是一种大端存储系统处理器,使用如图 4.3 所式的格式来访问存储器。地址 A 的字地址 A 的半字地址 A+1 的半字地址 A 的字节|地址 A+1 的字节地址 A+2 的字节|地址...