第14 章 触发器和时序逻辑电路 A 选择题 14

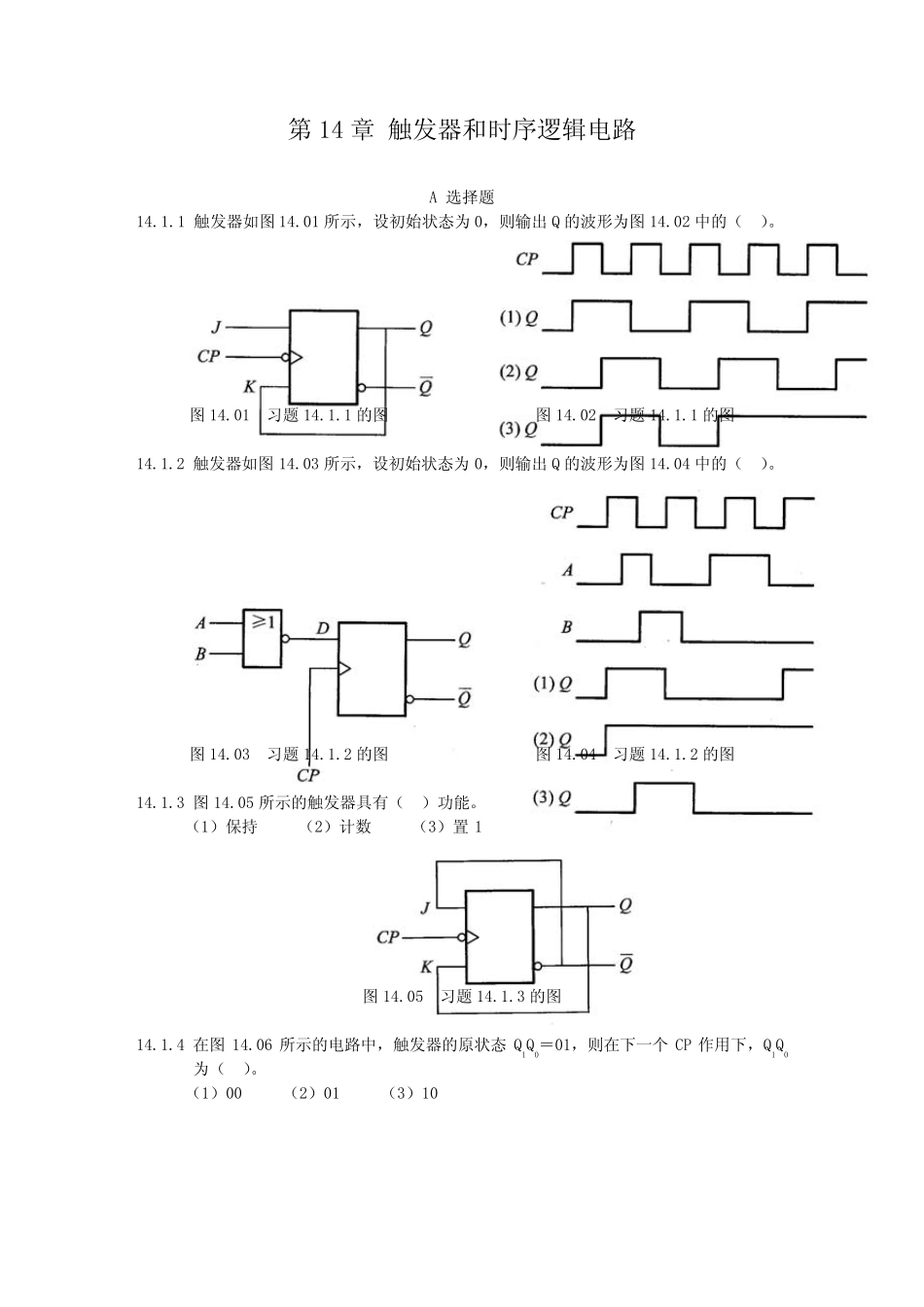

1 触发器如图14

01 所示,设初始状态为0,则输出Q 的波形为图14

02 中的( )

01 习题14

1 的图 图14

02 习题14

1 的图 14

2 触发器如图14

03 所示,设初始状态为0,则输出Q 的波形为图14

04 中的( )

03 习题14

2 的图 图14

04 习题14

2 的图 14

05 所示的触发器具有( )功能

(1)保持 (2)计数 (3)置 1 图14

05 习题14

3 的图 14

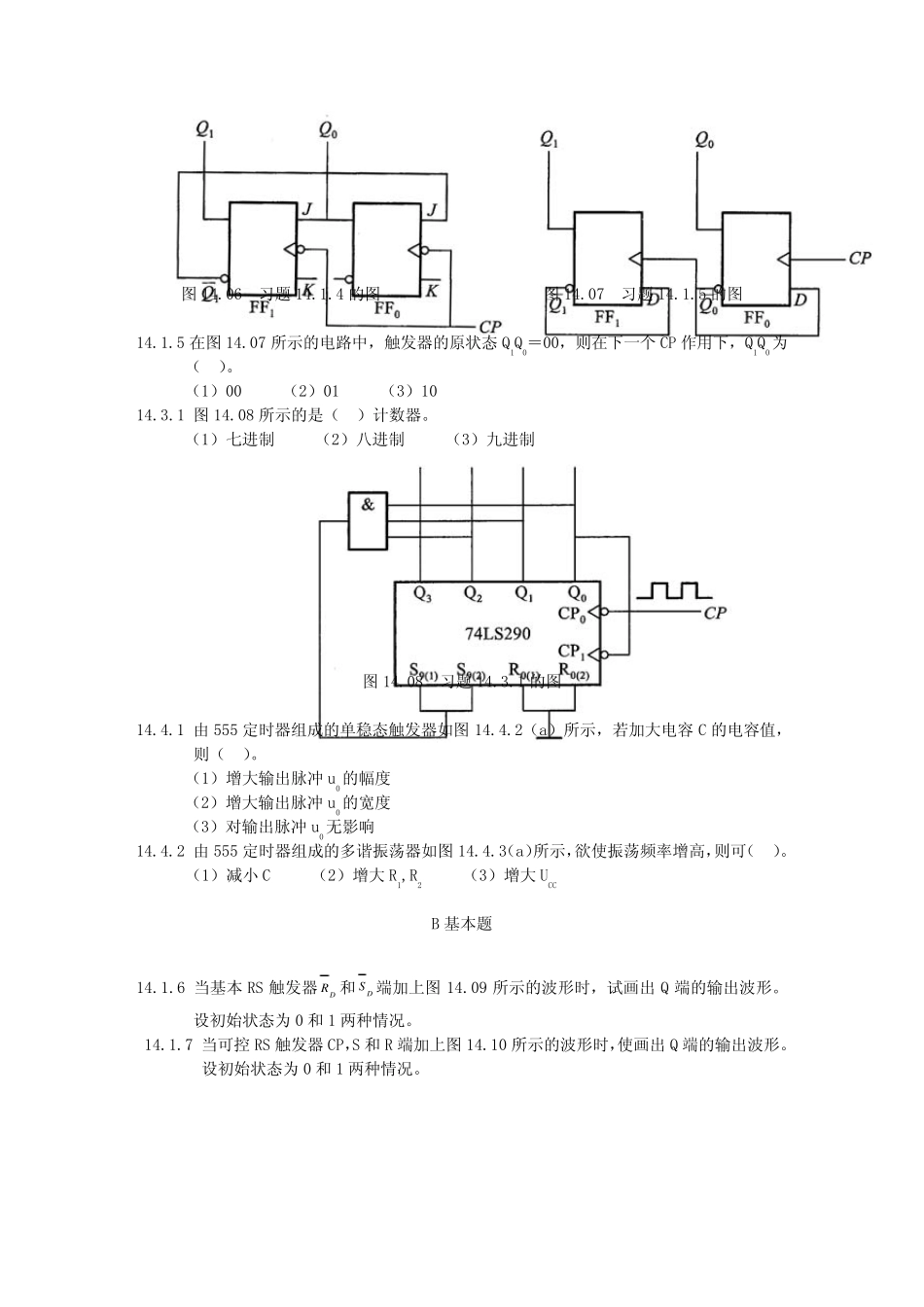

4 在图14

06 所示的电路中,触发器的原状态Q1Q0=01,则在下一个 CP 作用下,Q1Q0为( )

(1)00 (2)01 (3)10 图14

06 习题14

4 的图 图14

07 习题14

5 的图 14

5 在图14

07 所示的电路中,触发器的原状态Q1Q0=00,则在下一个CP 作用下,Q1Q0为( )

(1)00 (2)01 (3)10 14

08 所示的是( )计数器

(1)七进制 (2)八进制 (3)九进制 图14

08 习题14

1 的图 14

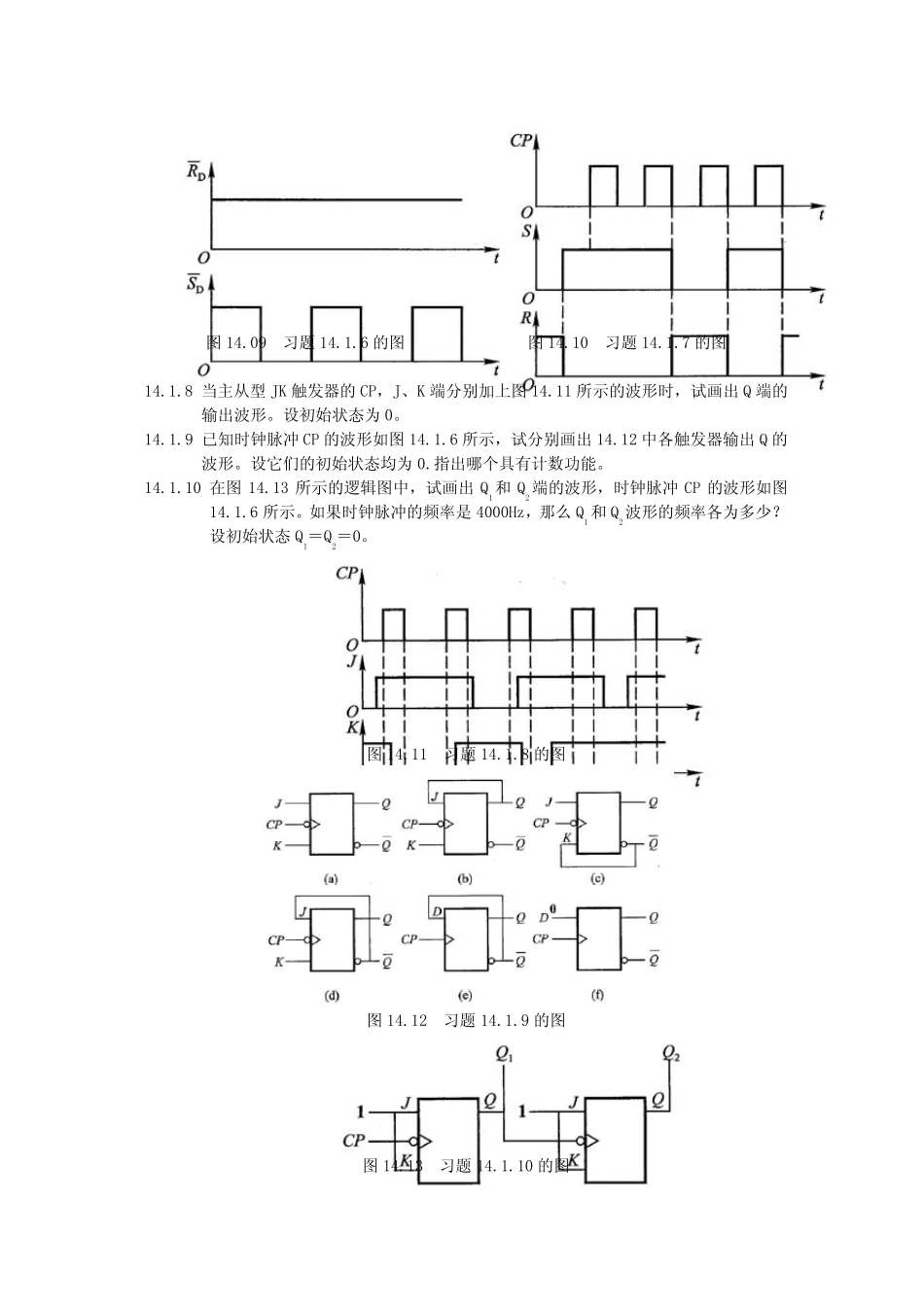

1 由 555 定时器组成的单稳态触发器如图14

2(a)所示,若加大电容 C 的电容值,则( )

(1)增大输出脉冲 u0的幅度 (2)增大输出脉冲 u0的宽度 (3)对输出脉冲 u0无影响 14

2 由 555 定时器组成的多谐振荡器如图14

3(a)所示,欲使振荡频率增高,则可( )

(1)减小 C (2)增大 R1,R2 (3)增大 UCC B 基本题 14

6 当基本 RS 触发器DR 和DS 端加上图14

09 所示的波形时,试画出 Q 端的输出波形

设初始状态为0 和 1 两种情况